Fractional-order Memristor Emulator with Multiple Pinched Points

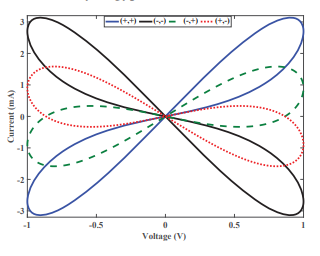

The paper proposes voltage-controlled first-and second-order memristor emulators. The emulators are designed using an operational-transconductance amplifier (OTA) and voltage multiplier blocks plus a fractional-order capacitor. The presented second-order emulator provides two pinched points controlled by order of the employed fractional-order capacitor. Numerical and PSPICE simulation results using AD844 and AD633 are introduced for different cases to validate the theoretical findings. The experimental verification is presented, showing the design flexibility and controllability based on the

Generalized α+β-order Filter Based on Single CCII

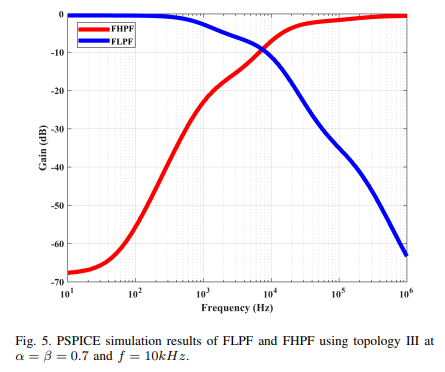

Different generalized filters topologies are proposed in the fractional-order domain. Three voltage-mode topologies and one current-mode topology are used to realize several types of fractional-order filters by applying different admittances combinations. The proposed topologies are designed using a single second-generation current conveyor (CCII-) and two fractional-order capacitors, which add more degrees of freedom for the design. The generalized Fractional Transfer Function (FTF) for each proposed topology is investigated where the fractional-order low-pass, band-pass, high-pass, and notch

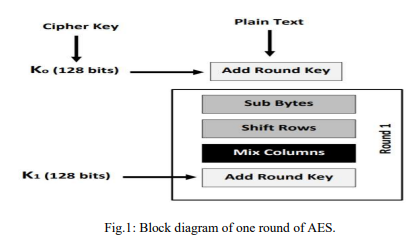

Generation of the chaotic keys on the fly for AES encryption system

This paper proposes a safe and effective method to generate the subkeys that are used in the Advanced Encryption Standard (AES) algorithm for data encryption applications. The suggested method relies upon the Pseudo-Random Number Generator (PRNG) that is created from the improved Lorenz chaotic system. The output of PRNG is exploited as a key schedule for generating AES subkeys where the output is characterized by having an infinite periodic length. This method can be used in high-speed applications since no hardware multipliers are utilized so it gives the best hardware performance

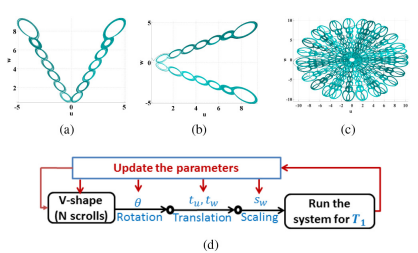

Design and FPGA Verification of Custom-Shaped Chaotic Attractors Using Rotation, Offset Boosting and Amplitude Control

This brief proposes a method of generating custom-shaped attractors, which depends on a planarly rotating V-shape multi-scroll chaotic system with offset boosting and amplitude control, and its FPGA verification. The proposed planarly rotating, translational (offset boostable), and scalable (amplitude controllable) system exhibits a wide basin of attraction and can cover the whole space. Consequently, non-autonomous parameters enable generating attractors of custom-shapes, e.g., letters of the English alphabet as a demonstrating example. Furthermore, non-autonomous parameters are employed to

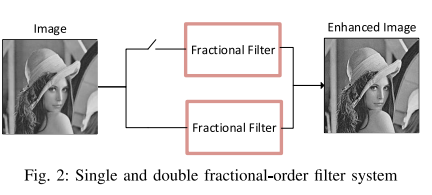

Double Fractional-order Masks Image Enhancement

Image enhancement is better achieved when fractional-order masks are used rather than integer-order ones, this is due to the flexibility of fractional-order parameters control. This paper proposes a combination of fractional-order masks to be used in parallel as double filters system structure to improve image enhancement rather than using a single-stage filter. Various performance metrics are used in this work to evaluate the proposed system, such as Information Entropy (IE), Average Gradient (AG), Structural Similarity Index Metric (SSIM) and Peak Signal to Noise Ratio (PSNR). Based on

Fractional-order synchronization of two neurons using Fitzhugh-Nagumo neuron model

This paper studies the synchronization of two coupled neurons using Fitzhugh-Nagumo model in the fractional-order domain. In general, studying systems in the fractional-order domain provides a wider scope view of their behavior. When the neuron is generalized into the fractional-order domain, the normal behaviors displayed in the integer case change. Furthermore, two neurons display various synchronization patterns. The neurons' fractional-order system is solved using non-standard finite difference scheme together with Grunwald-Letnikov discretization. © 2016 IEEE.

FPGA implementation of fractional-order Chua's chaotic system

This paper introduces FPGA implementation of fractional order double scrolls chaotic system based on Chua circuit. Grunwald-Letnikov's (GL) definition is used to generalize the chaotic system equations into the fractional-order domain. Xilinx ISE 14.5 is used to simulate the proposed design and Artix-7 XC7A100T FPGA is used for system realization. Experimental results are presented on digital oscilloscope and the error between theoretical and experimental results is calculated. Also, various interesting attractors are obtained with respect to different parameters values and window sizes. Some

CFOA-Based fractional order simulated inductor

In this paper, a generalized fractional-order form of the simulated inductor using a single current feedback operational amplifier (CFOA) and a fractional-order capacitor is introduced. Analytical expression of the equivalent fractionalorder inductor versus the circuit elements is achieved. Moreover, the effect of the parasitic impedance and the non-idealities of the CFOA are investigated analytically with numerical simulations and circuit equivalent. Circuit simulations are discussed using AD844 spice model to validate the theoretical study of the fractional-order inductor. Simulations show

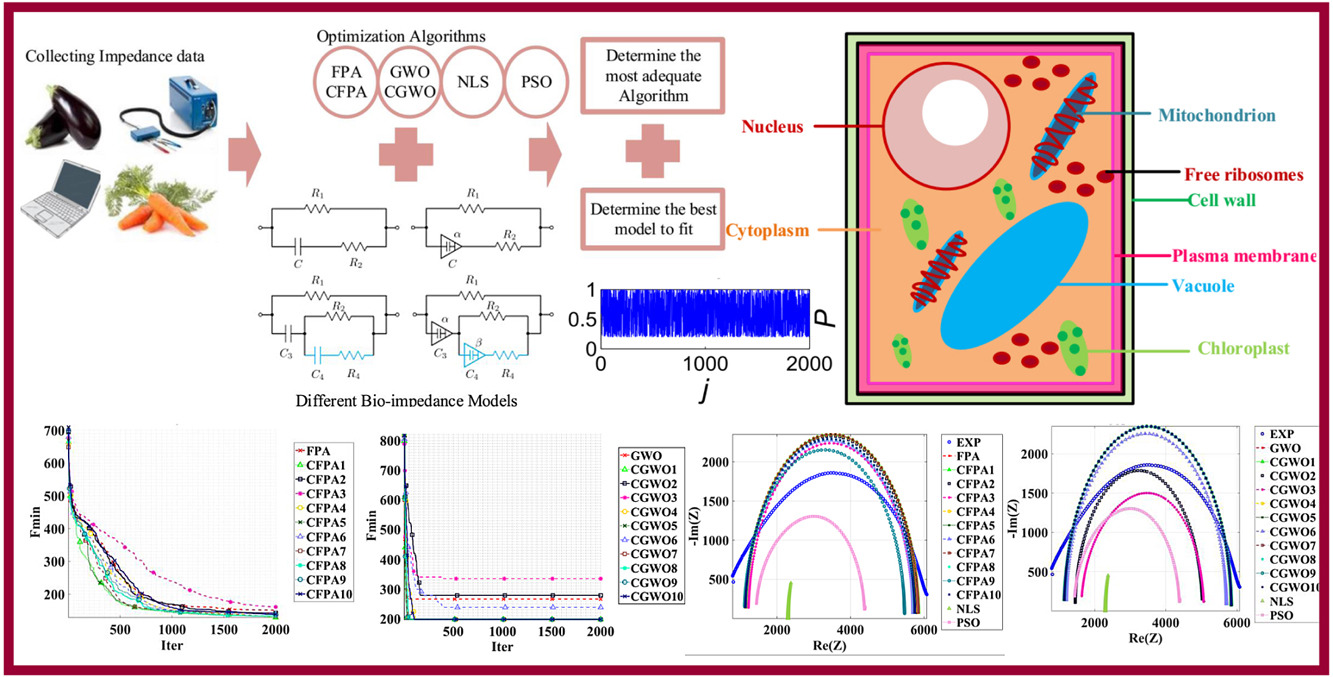

Chaotic Flower Pollination and Grey Wolf Algorithms for parameter extraction of bio-impedance models

Precise parameter extraction of the bio-impedance models from the measured data is an important factor to evaluate the physiological changes of plant tissues. Traditional techniques employed in the literature for this problem are not robust which reflects on their accuracy. In this paper, the Flower Pollination Algorithm (FPA), the Grey Wolf Optimizer (GWO) and ten of their chaotic variants are employed to extract the parameters of bio-impedance models. These models are the simplified Hayden and Double-Shell models in their integer and fractional order forms. Experimental data sets of three

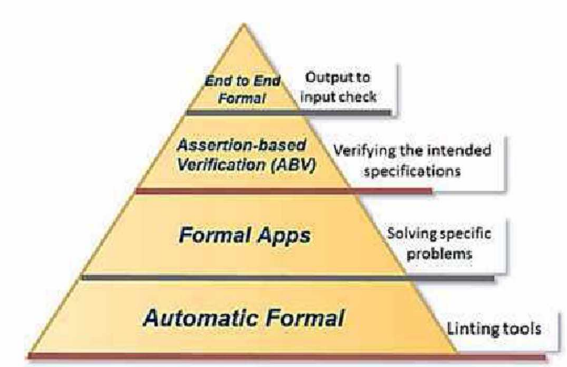

Automatic RTL coding correction Linting tool for critical issues

This paper posits an automatic handling to some of the most common RTL critical issues in the verification process. In this paper, we propose an automatic linting tool to handle some causes of intentional latches generated in the synthesis process and clock gating timing violation. Therefore, no need to waste verification time to dive through long codes to handle them manually. The proposed tool has been implemented using python to speed up the linting process with easy GUI. Finally, it has been tested on OpenCore certificated projects source codes. © 2018 IEEE.

Pagination

- Previous page ‹‹

- Page 54

- Next page ››