A novel 4-D hyperchaotic system with two quadratic nonlinearities and its adaptive synchronisation

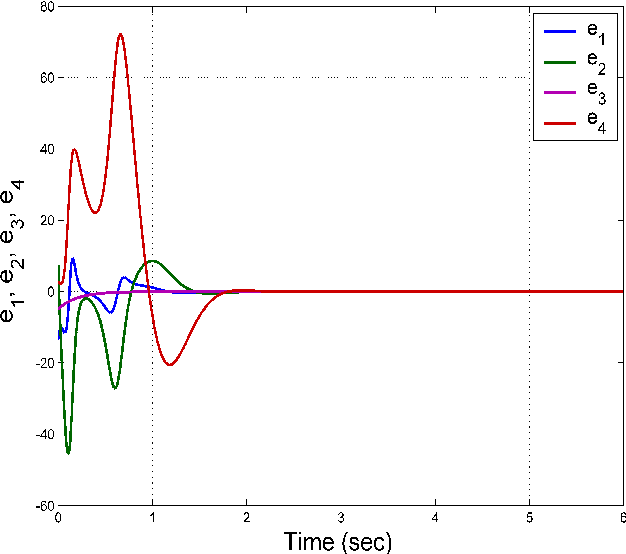

This work announces an eleven-term novel 4-D hyperchaotic system with two quadratic nonlinearities. A qualitative analysis of the properties of the novel 4-D hyperchaotic system is presented. A special feature of our novel hyperchaotic system is that it has three equilibrium points of which two are unstable and one is locally asymptotically stable. The Lyapunov exponents of the novel hyperchaotic system are obtained as L1 = 1.5146, L2 = 0.2527, L3 = 0 and L4 = −12.7626. The Kaplan-Yorke dimension of the novel hyperchaotic system is derived as DKY = 3.1385. Next, this work describes the design

Partial fraction expansion–based realizations of fractional-order differentiators and integrators using active filters

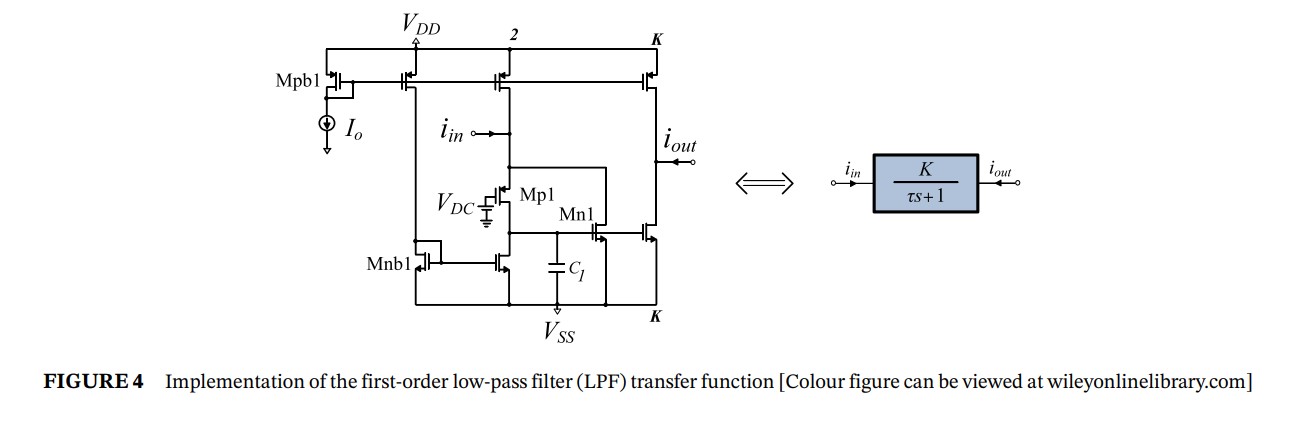

Approximations of the fractional-order differentiator and integrator operators s±r are proposed in this work. These approximations target the realization of these operators using standard active filter transfer functions. Hence, circuit implementations in integrated circuit form or in discrete component form are significantly facilitated. Complementary metal-oxide-semiconductor (CMOS) realizations of the proposed approximations are given and validated via simulations using the AMS 0.35 μm CMOS technology, while experimental results using operational amplifier circuits are tested and confirm

Active circuit model of low-frequency behavior in perovskite solar cells

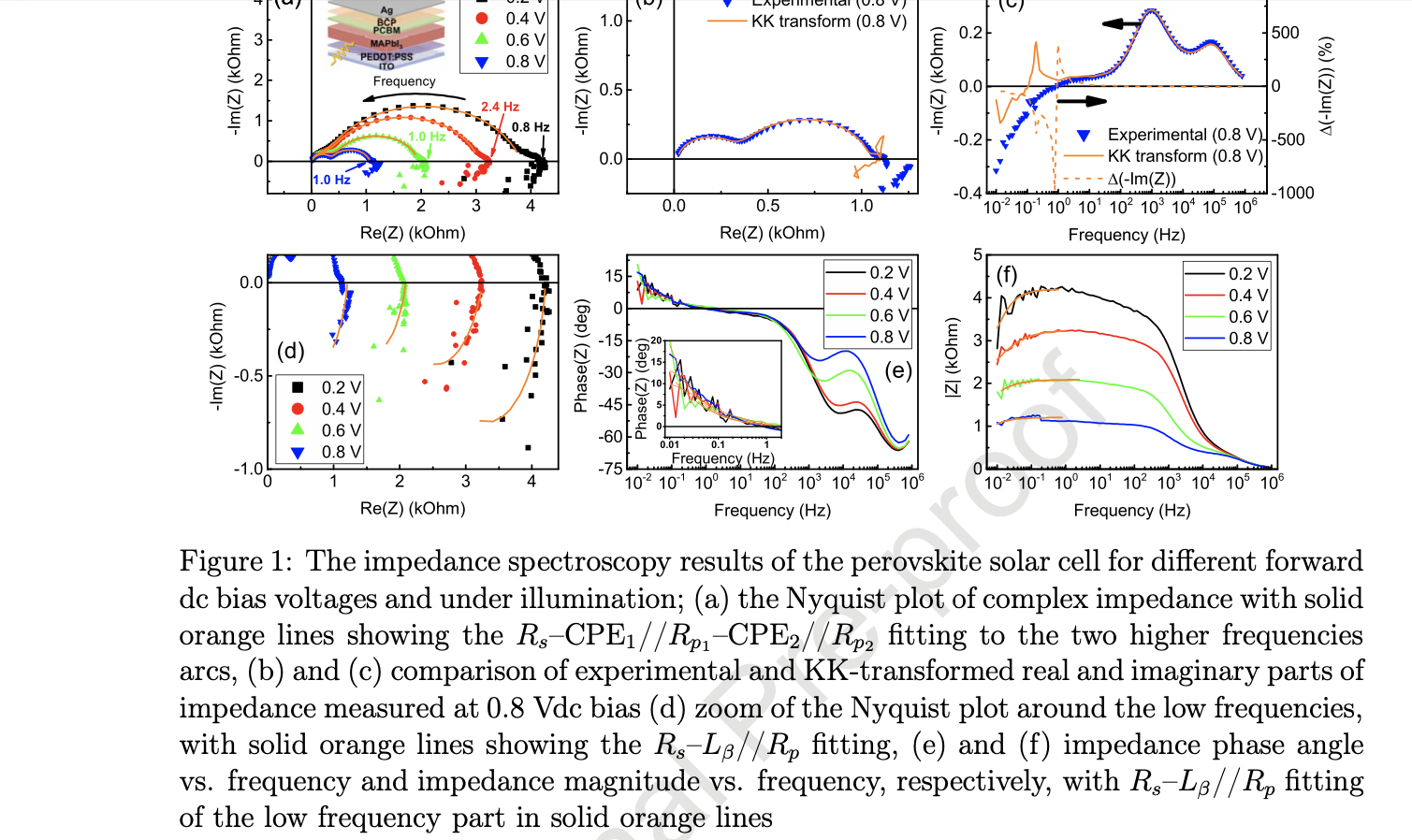

The low-frequency impedance hook in perovskite solar cells (PSC) is a feature that has been frequently associated with the behavior of passive circuits of inductors or negative capacitances. However, if the experimental impedance data do not transform according to the Kramers-Kronig (KK) relations, the system does not fulfill the conditions of linearity, stability, causality and finiteness necessary for validating the impedance measurements and fitting it using passive circuit elements. In this study, we found that the impedance hook in a standard PSC configuration is not compliant with the KK

Accurate timing analysis of combinational logic cells engine using adaptive technique based on current source model

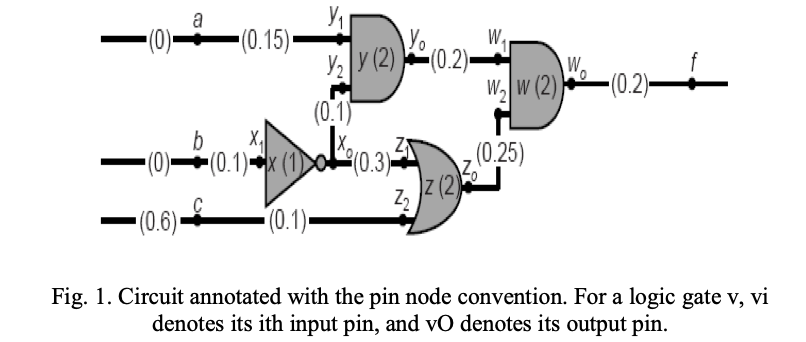

As the usage of very large scale integration (VLSI) in computers continues to increase, debugging of timing problems on actual hardware becomes more and more difficult. The post-layout gate-level simulation constitutes a critical design step for timing closure. The major drawback of traditional post-layout gate-level simulation is its long analysis time, which increases as design complexity increases. An alternative method is static timing analysis (STA), which can reduce analysis time. Going deeper through the nanometer technology, new STA techniques have to be present to provide more

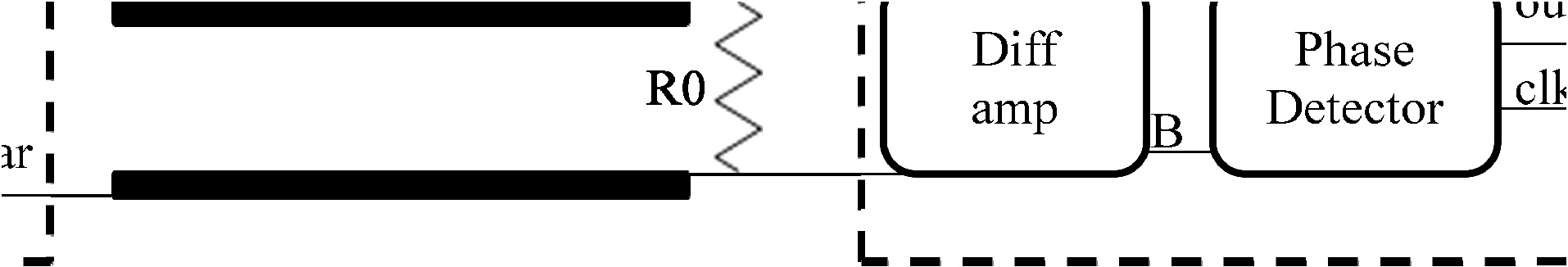

A new signaling technique for a low power on-chip SerDes transceivers

This paper represents a new self timed signaling technique for low power SerDes transceiver. A three level coding technique enables extracting the clock from the data using simple phase detector rather than using complex power hungry blocks such as Clock Data Recovery (CDR) or a Phase Locked Loop (PLL). This SerDes transceiver was implemented using 90nm TSMC technology. The transmitter serializes 8 parallel bits at 1.125GHz, and multiplexes the 10Gbps serial data stream with a 20GHz clock on a single line using three level signaling. The total power consumed in the Tx/Rx pair with the

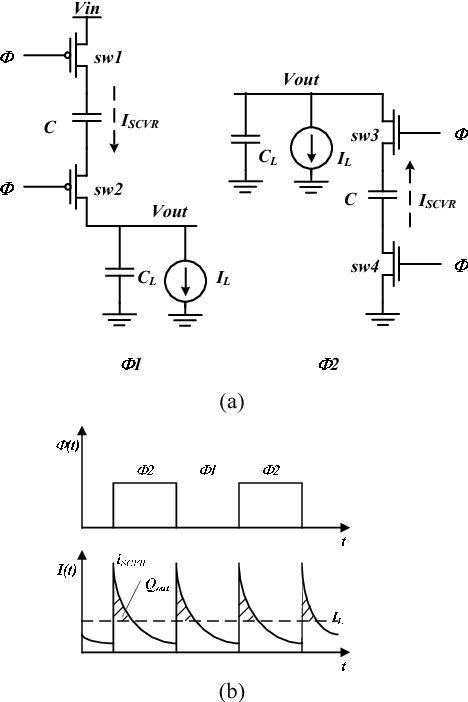

A novel control technique to eliminate output-voltage-ripple in switched-capacitor DC-DC converters

A novel ripple mitigation technique is proposed for switched-capacitor voltage regulators (SCVR), which eliminates the output voltage ripple without using multi-phase interleaving. An inner control loop matches the SCVR's switch current to the load current on a cycle by cycle basis. A 2-phase 32 SCVR is designed in 45-nm CMOS process with the proposed control. For a 1.8 V to 1.05 V /40 mA converter, the proposed mitigation loop reduces the peak-to-peak output ripple from 330 mVp-p to 17 mVp-p, using total output capacitance of 4 nF/A. In addition, the proposed technique yields excellent

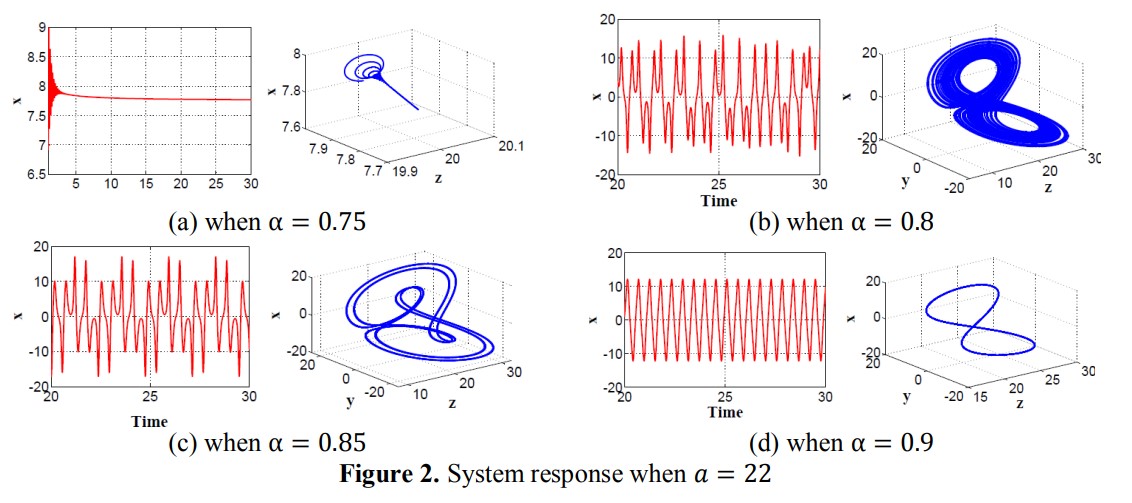

Parametric control on fractional-order response for Lü chaotic system

This paper discusses the influence of the fractional order parameter on conventional chaotic systems. These fractional-order parameters increase the system degree of freedom allowing it to enter new domains and thus it can be used as a control for such dynamical systems. This paper investigates the behaviour of the equally-fractional-order Lü chaotic system when changing the fractional-order parameter and determines the fractional-order ranges for chaotic behaviour. Five different parameter values and six fractional-order cases are discussed through this paper. Unlike the conventional

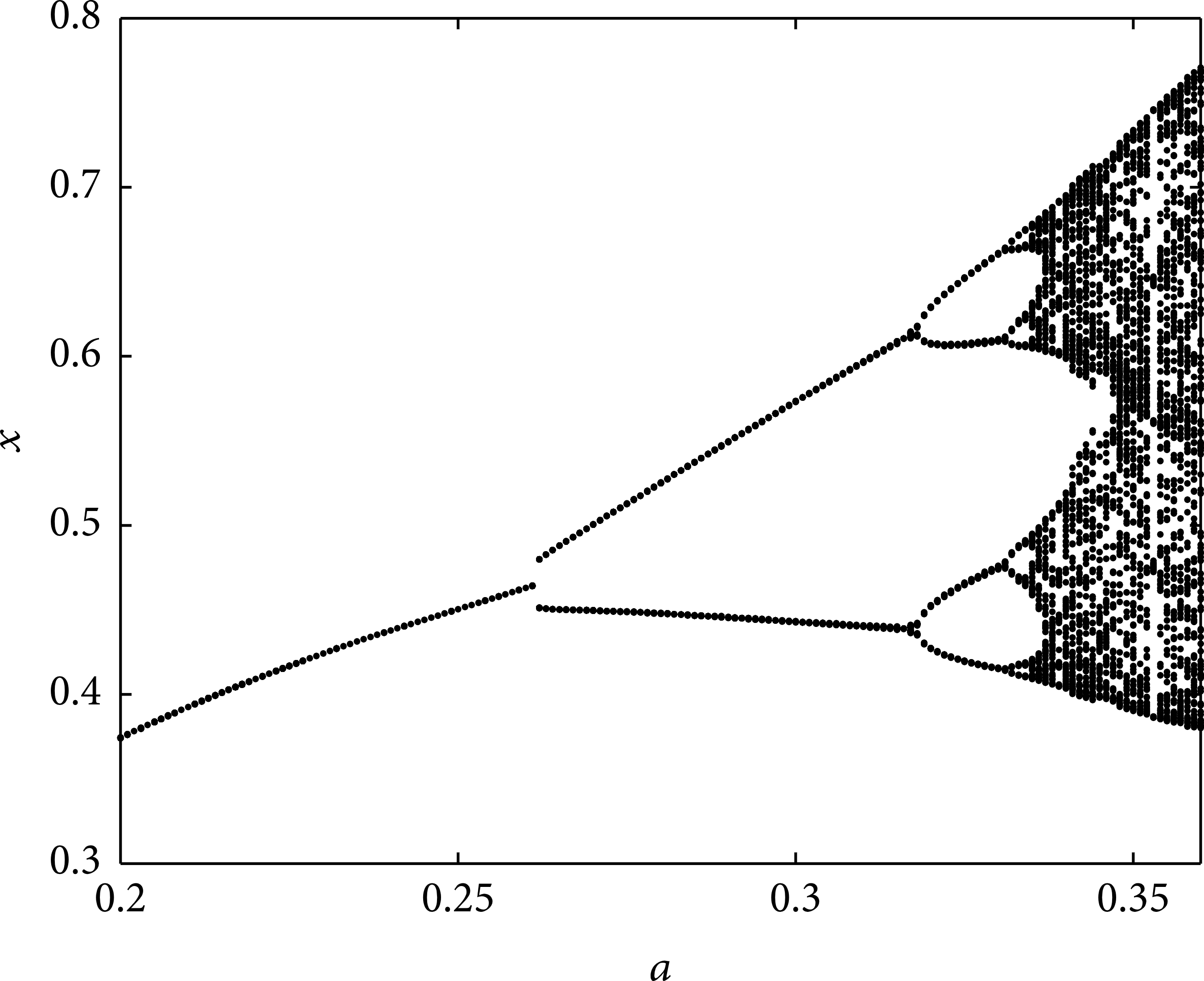

A novel chaotic system without equilibrium: Dynamics, synchronization, and circuit realization

A few special chaotic systems without unstable equilibrium points have been investigated recently. It is worth noting that these special systems are different from normal chaotic ones because the classical Shilnikov criterion cannot be used to prove chaos of such systems. A novel unusual chaotic system without equilibrium is proposed in this work. We discover dynamical properties as well as the synchronization of the new system. Furthermore, a physical realization of the system without equilibrium is also implemented to illustrate its feasibility. © 2017 Ahmad Taher Azar et al.

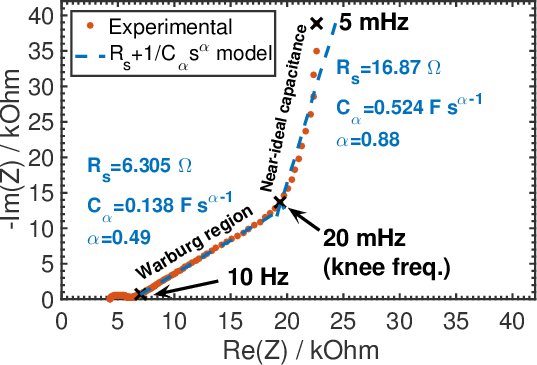

Variability of supercapacitor fractional-order parameters extracted from discharging behavior using least squares optimization

In this paper the variability of supercapacitor fractional-order model parameters are explored when extracted using a non-linear least squares optimization applied to their constant current discharging behaviour. The variability of parameters extracted 1000 different times applying the optimization process to multiple sets of simulated and experimental data are presented to validate this approach. The experimental results were collected from 4 samples of Panasonic EEC-SSR5H105 supercapacitors (1 F rating) acting as a secondary power source for an Arduino Uno system. Simulations using the

Fractional-order mihalas-niebur neuron model implementation using current-mirrors

A simple realization of the fractional-order Mihalas-Niebur neuron model is presented in this work. The required low-pass filter is implemented using current-mirrors offering simple circuitry and, also, electronic tunability of the realized time-constant. Due to the limited bandwidth required for this application, the necessary fractional-order capacitor is realized using an appropriately configured second-order RC network. The proposed realization highlights the connection between the fractional-order and the frequency spiking of the model through appropriate simulation results, which are

Pagination

- Previous page ‹‹

- Page 42

- Next page ››