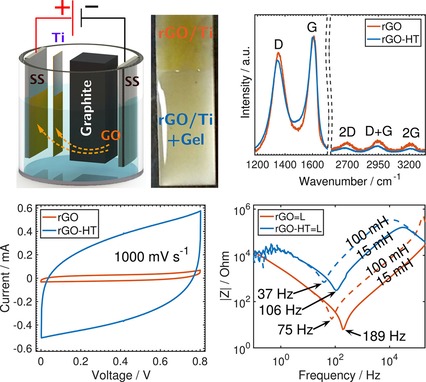

All-Solid-State Double-Layer Capacitors Using Binderless Reduced Graphene Oxide Thin Films Prepared by Bipolar Electrochemistry

Bipolar electrochemistry is used as an economical, single-step, and scalable process for the oxidation of a wireless graphite substrate, and the subsequent electrophoretic deposition of graphene oxide thin film on a second wireless substrate. An all-solid-state symmetric double-layer capacitor (EDLC) using binderless reduced graphene oxide electrodes exhibited outstanding reversibility and capacitance retention over 18000 cycles, as well as superior capacitive behavior at far-from-dc frequencies (for example 45 and 47 µ F cm-2), effective capacitances at 75 and 189 Hz, respectively (computed

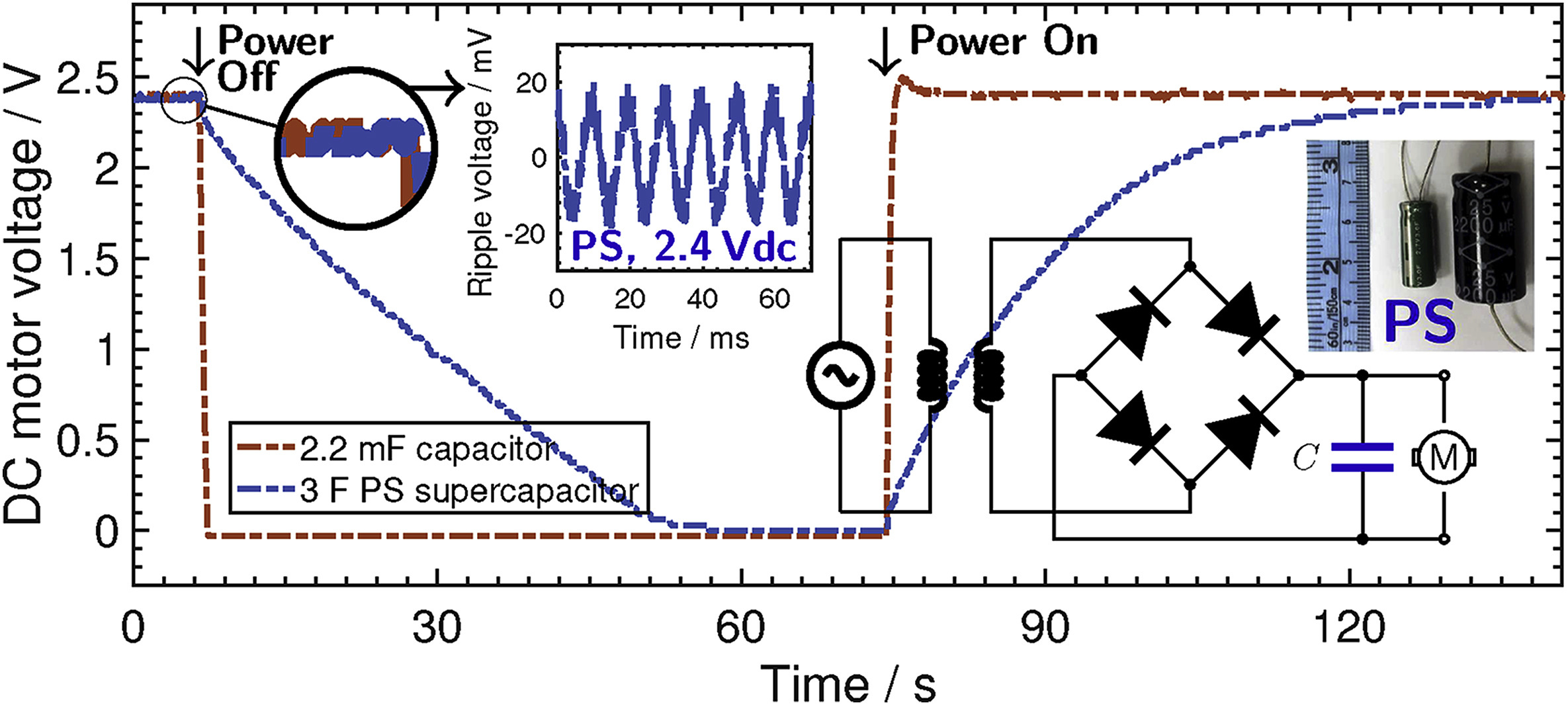

Capacitive behavior and stored energy in supercapacitors at power line frequencies

Supercapacitors are commonly viewed and mainly employed as dc electrical energy storage devices. Their behavior at far-from-dc is usually overlooked and not well explored for potential applications. In this work, we investigate analytically and experimentally the performance of supercapacitor at high frequencies, including the 50 Hz/60 Hz power line frequencies. The variation of effective capacitance, power and energy with frequency are analyzed using a fractional-order model consisting of a series resistance and a constant phase element for both pure sinusoidal and full-wave rectified voltage

Commercial supercapacitor parameter estimation from step voltage excitation

Supercapacitors are crucial elements in advanced industrial electronic systems particularly when supplied from renewable energy sources. Here, we derive expressions for the current, power, and stored energy in a supercapacitor excited with a step voltage signal. Although, it is not common practice to charge supercapacitors using a step voltage, these devices are sometimes used in switching-type applications where they are subject to this type of signal. We validate the derived mathematical expression of the current via experiments on four different commercial devices. By fitting the measured

Simple implementations of fractional-order driving-point impedances: Application to biological tissue models

A novel procedure for the circuit implementation of the driving-point impedance of frequency-domain material models, constructed from fractional-order elements of arbitrary type and order, is introduced in this work. Following this newly introduced concept, instead of emulating separately each fractional-order element in the model under consideration, the direct emulation of the complete model can be achieved through the approximation of the total impedance function. The magnitude and phase frequency responses of the impedance function are first extracted and approximated through curve-fitting

High Speed, Approximate Arithmetic Based Convolutional Neural Network Accelerator

Convolutional Neural Networks (CNNs) for Artificial Intelligence (AI) algorithms have been widely used in many applications especially for image recognition. However, the growth in CNN-based image recognition applications raised challenge in executing millions of Multiply and Accumulate (MAC) operations in the state-of-The-Art CNNs. Therefore, GPUs, FPGAs, and ASICs are the feasible solutions for balancing processing speed and power consumption. In this paper, we propose an efficient hardware architecture for CNN that provides high speed, low power, and small area targeting ASIC implementation

Hermite polynomials in the fractional order domain suitable for special filters design

Due to the importance of its integer order counterpart in many mathematical and engineering fields, the fractional order Hermite polynomials are studied in this paper. A fractional variation of the well known Hermite differential equation is introduced based on Caputo fractional operator. The proposed equation is solved using fractional Taylor power series method and the convergence is verified using truncated series for different values of the parameters. The condition for fractional polynomial solution is obtained and the first four polynomials are scaled using an appropriate scaling factor

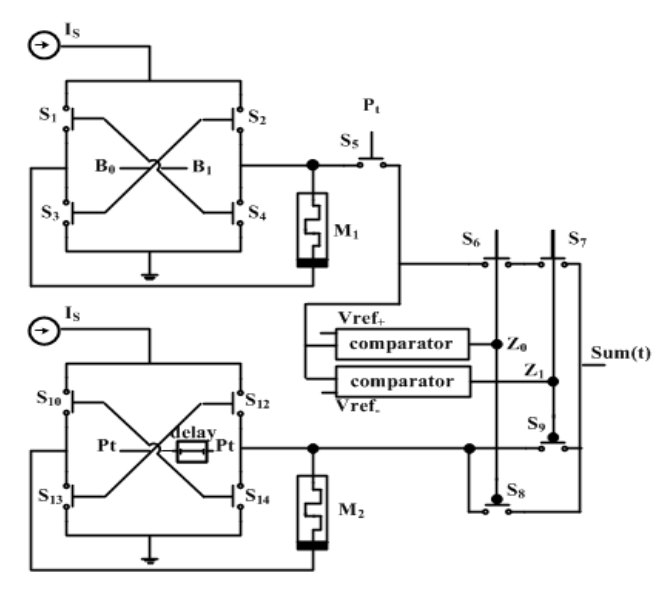

Memristor-based redundant binary adder

This paper introduces a memristor based redundant binary adder for canonic signed digit code, that coding eliminates the carry and provides a carry-free addition. The proposed binary adder circuit tries to achieve high addition speed that is independent on the length of the data using the accumulation property of a Nano-element called a memristor. The general block diagram of the proposed circuit is illustrated based on memristors and its operation has been validated using HP memristor model and simulated via different examples using PSPICE showing a great match. © 2014 IEEE.

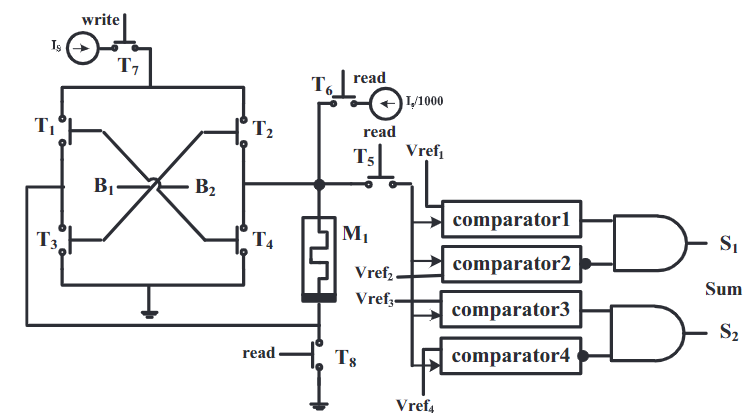

Memristor based N-bits redundant binary adder

This paper introduces a memristor based N-bits redundant binary adder architecture for canonic signed digit code CSDC as a step towards memristor based multilevel ALU. New possible solutions for multi-level logic designs can be established by utilizing the memristor dynamics as a basis in the circuit realization. The proposed memristor-based redundant binary adder circuit tries to achieve the theoretical advantages of the redundant binary system, and to eliminate the carry (borrow) propagation using signed digit representation. The advantage of carry elimination in the addition process is that

Memristor-based pulse width modulator circuit

This paper discusses the use of the memristor in one of the most important modulation techniques in communication field namely the pulse-width modulation. A fundamental two designs for memristor-based lead and trail PWM are discussed with mathematical analysis and PSPICE simulation results which show a great matching with the analytical formulation. Moreover, a third design which combine those two designs to generate a more accurate memristor-based center PWM is discussed with the appropriate analysis, numerical and PSPICE simulation results. The simulation results matches the theoretical

Hardware Speech Encryption Using a Chaotic Generator, Dynamic Shift and Bit Permutation

This paper proposes a speech encryption and decryption system, its hardware architecture design and FPGA implementation. The system utilizes Nosé Hoover chaotic generator and/or dynamic shift and bit permutation. The effect of different blocks in the proposed encryption scheme is studied and the security of the system is validated through perceptual and statistical tests. The complete encryption scheme is simulated using Xilinx ISE 14.5 and realized on FPGA Xilinx Kintex 7, presenting the experimental results on the oscilloscope. The efficiency is also validated through hardware resources

Pagination

- Previous page ‹‹

- Page 16

- Next page ››