Breadcrumb

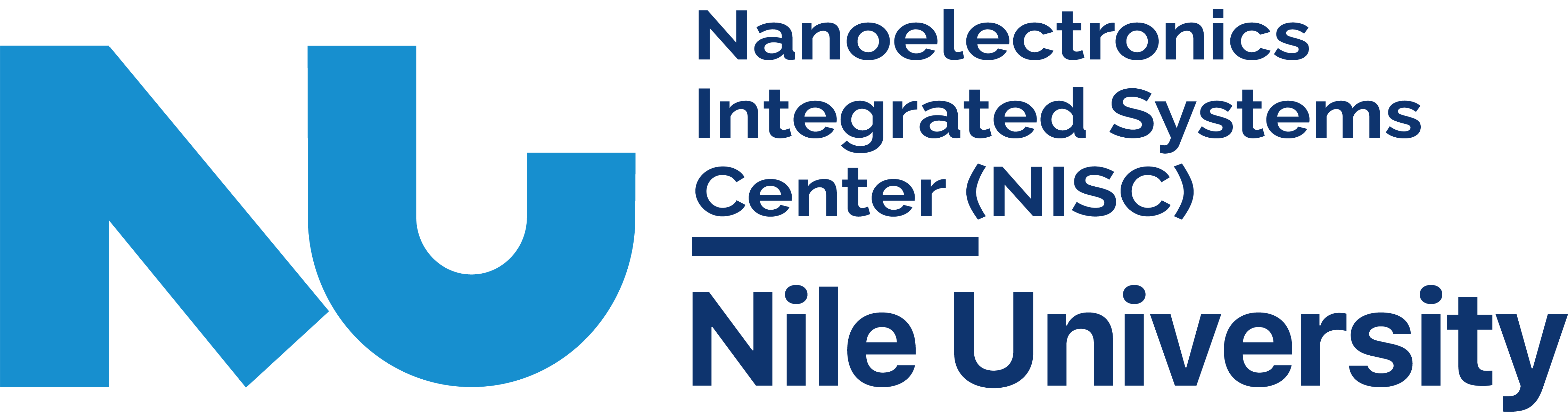

Generalized smooth transition map between tent and logistic maps

There is a continuous demand on novel chaotic generators to be employed in various modeling and pseudo-random number generation applications. This paper proposes a new chaotic map which is a general form for one-dimensional discrete-time maps employing the power function with the tent and logistic maps as special cases. The proposed map uses extra parameters to provide responses that fit multiple applications for which conventional maps were not enough. The proposed generalization covers also maps whose iterative relations are not based on polynomials, i.e. with fractional powers. We introduce

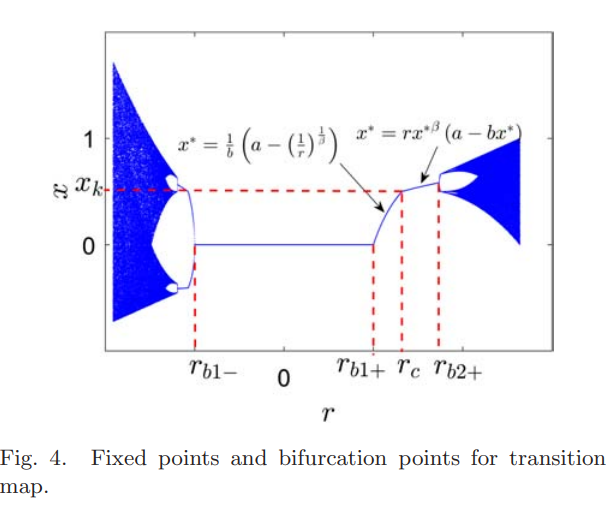

Parameterized test patterns methodology for layout design rule checking verification

Design rules verification is an essential stage in the Process Design Kit (PDK) release for any fab. Since achieving high yield is the target of any fab, the design rules should ensure this. Design rules violations happening after fabrication lead to disastrous results on the mask sets as well as increased cost and delayed schedules. Here comes the importance of verifying these design rules and making sure that they represent the process in a manner that achieves a high yield and detects design rules issues early on. The verification process consumes 60% of the release cycle and the most time

2T2M memristor-based memory cell for higher stability RRAM modules

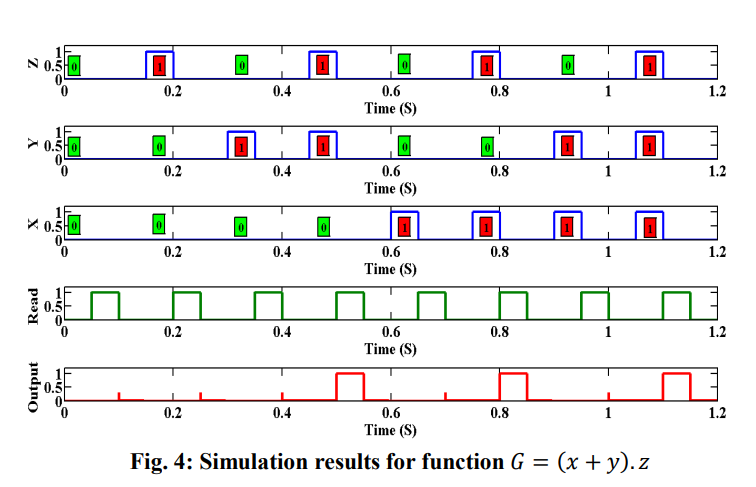

This paper introduces a novel 2T2M memristor based memory cell which, offers higher stability and noise margins than previous works. The proposed 2T2M RRAM module is similar to conventional 6T SRAM module in terms of delay and number of interface pins. However, the predicted area of the proposed 2T2M RRAM cell is significantly lower compared to the CMOS based 6T SRAM cell, and is also expected to consume lower energy. The nonvolatile characteristics of the cell make it more attractive for nonvolatile random access memory design. Write, read and repeated read operations of the proposed 2T2M

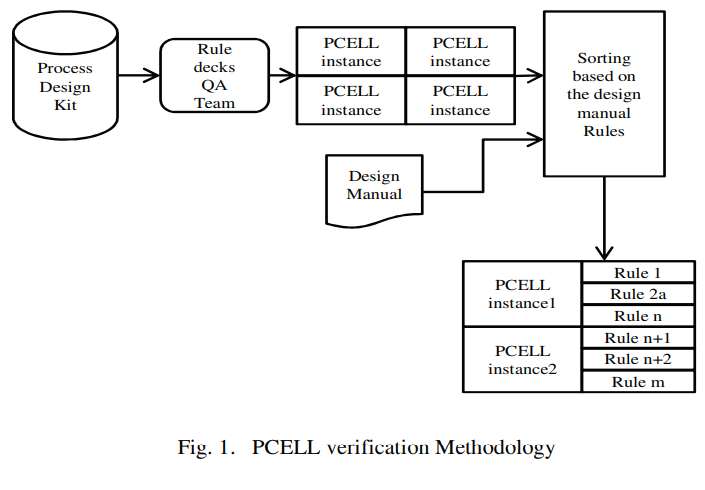

Memristor-MOS hybrid circuit redundant multiplier

This paper introduces a step forward towards memristor-MOS hybrid circuit to achieve any combinational function. The proposed design is based on reducing the area by replacing the complete pull-down network with just one memristor and one comparator. The concept is then verified using an example of a simple function. Also, a proposed architecture for memristor based redundant multiplier circuit is introduced and verified using the SPICE simulation. Therefore, any redundant functions can be implemented using the same concept. © 2014 IEEE.

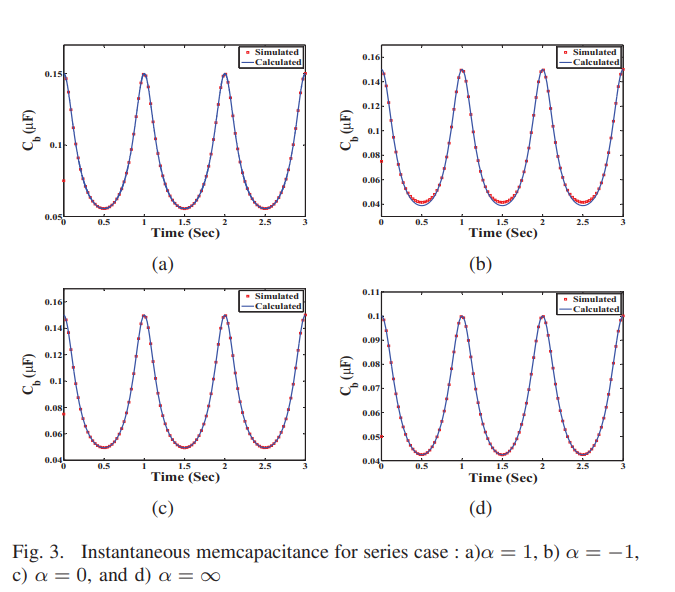

On the mathematical modeling of series and parallel memcapacitors

Recently, Memristive elements such as memristor, memcapacitor and meminductors have become very attractive components in many applications, due to its unique behavior which can not be obtained using the other conventional elements. This paper discusses the analytical analysis of two memcapacitors connected in series and in parallel taking the effect of mismatch in mobility factor and polarity of each one. The obtained formulas of instantaneous memcapacitance for each memcapacitor are derived and four special cases are analyzed in more details. The proposed special cases are validated using

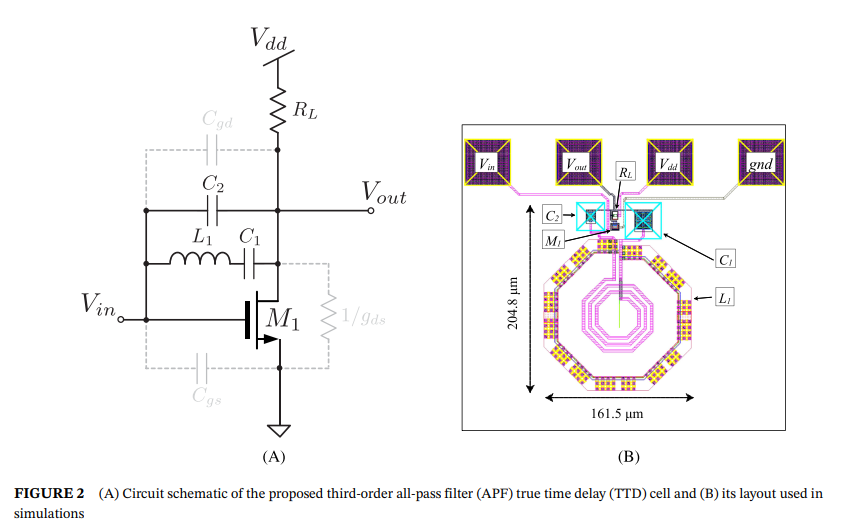

Wideband third-order single-transistor all-pass filter

In this letter, a third-order wideband voltage-mode all-pass filter (APF) is proposed for application as a true time delay (TTD) cell. The advantages of designing a single-stage higher order filter over cascading several lower order stages are illustrated. The proposed APF circuit is based on a single metal-oxide-semiconductor (MOS) transistor and is canonical because it requires one resistor, one inductor, and two capacitors. To the best of the authors' knowledge, this is the first single-transistor third-order APF circuit to be reported in the literature. The operation of the proposed APF is

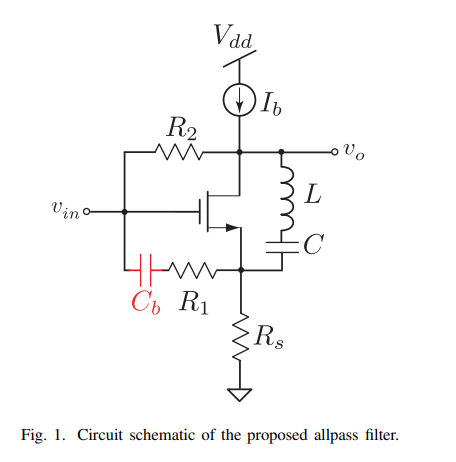

8-GHz low-power voltage-mode second-order allpass filter in 65-nm CMOS

In this paper, a CMOS wide-band low-power second-order voltage-mode allpass filter design is proposed as a true time delay element. The proposed allpass filter core design consists of a single transistor, three resistors, one capacitor and one inductor. As a time delay element, the proposed circuit exhibits a group delay of 34 ps within a bandwidth of 8 GHz while consuming only 926 μW from a 1-V supply voltage. The proposed filter was designed in 65-nm CMOS technology and verified through post-layout simulation results. © 2019 IEEE.

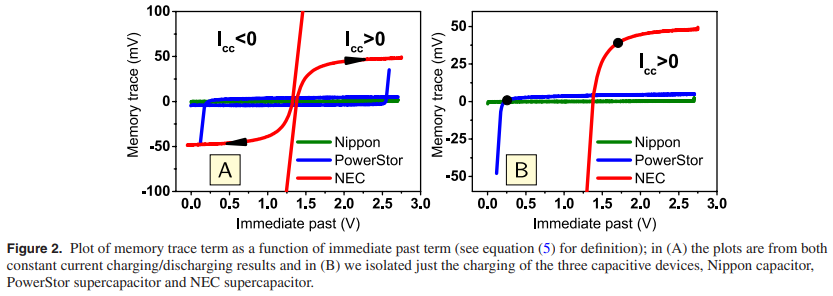

Quantification of memory in fractional-order capacitors

In this study we quantify and interpret the inherent memory in fractional-order capacitors when subjected to constant current charging/discharging waveforms. This is done via a finite difference approximation of the fractional order rate equation I(t) = Cαdαv(t)/dtα (0 le; α ≤ 1) relating current to voltage in these devices. It is found that as the fractional exponent α decreases, the weight of the voltage memory trace that results from the contribution of past voltage activity increases, and thus the measured response of the device at any time is increasingly correlated to its past. Ideal

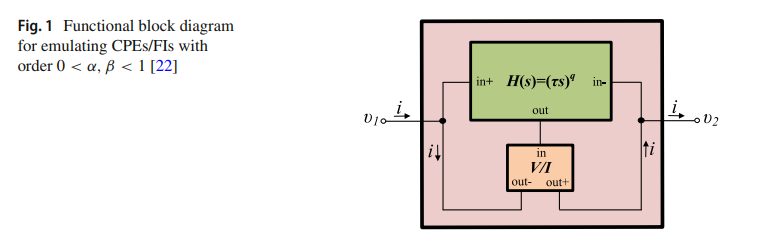

Generalized Fully Adjustable Structure for Emulating Fractional-Order Capacitors and Inductors of Orders less than Two

A novel scheme suitable for the emulation of fractional-order capacitors and inductors of any order less than 2 is presented in this work. Classically, fractional-order impedances are characterized in the frequency domain by a fractional-order Laplacian of the form s± α with an order 0 < α< 1. The ideal inductor and capacitor correspond, respectively, to setting α= ± 1. In the range 1 < α< 2 , fractional-order impedances can still be obtained before turning into a Frequency- Dependent Negative Resistor (FDNR) at α= ± 2. Here, we propose an electronically tunable fractional-order impedance

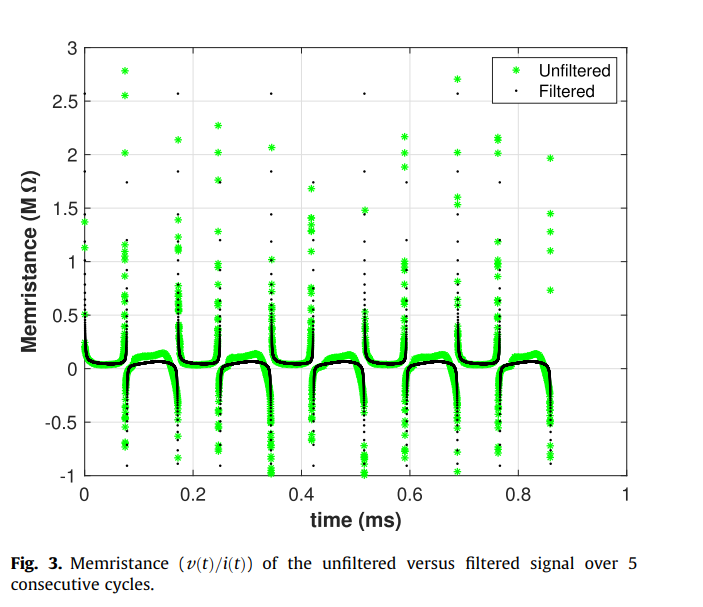

On the mechanism of creating pinched hysteresis loops using a commercial memristor device

In this short communication we analyze the impact of signal harmonics on the formation of the pinched hysteresis loop using a commercial memristor device. We show that by using only the fundamental frequency and the second harmonic components, extracted from the measured electrical current signal, a distortion-less pinched hysteresis loop is re-created. This loop is then used to simulate memristor-based AND/OR gates without any loss in digital functionality. This verifies that the generation of a pinched hysteresis loop requires a nonlinear frequency doubling mechanism to create a second

Pagination

- Previous page ‹‹

- Page 19

- Next page ››