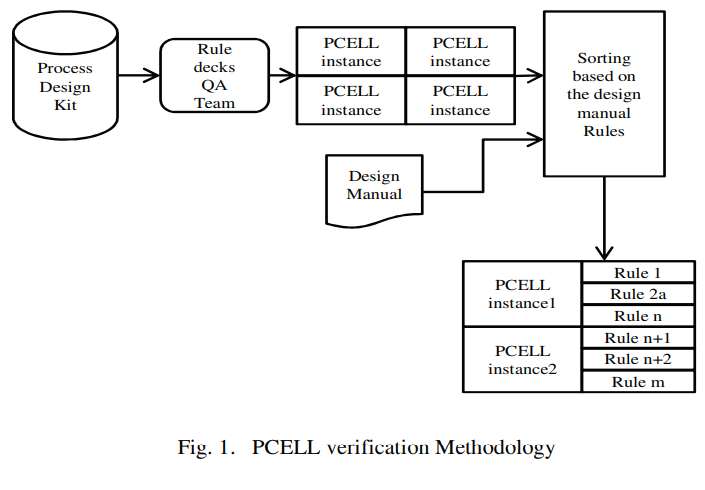

Parameterized test patterns methodology for layout design rule checking verification

Design rules verification is an essential stage in the Process Design Kit (PDK) release for any fab. Since achieving high yield is the target of any fab, the design rules should ensure this. Design rules violations happening after fabrication lead to disastrous results on the mask sets as well as increased cost and delayed schedules. Here comes the importance of verifying these design rules and making sure that they represent the process in a manner that achieves a high yield and detects design rules issues early on. The verification process consumes 60% of the release cycle and the most time consuming step in the process is the Design rules checking (DRC) verification. Advanced technology nodes introduced stricter design rules as well as new design techniques, which added more complexity to the design rules development and verification. This paper presents a novel flow for automating the most time consuming part of the (DRC) rule decks verification, which is test cases creation and allows users to enhance the quality of the verification process and increase the testing coverage as well. And eventually reduces the time consumed in verification to 26% of what it was using conventional verification methods. © 2015 IEEE.