Motion and depth augmented semantic segmentation for autonomous navigation

Motion and depth provide critical information in autonomous driving and they are commonly used for generic object detection. In this paper, we leverage them for improving semantic segmentation. Depth cues can be useful for detecting road as it lies below the horizon line. There is also a strong structural similarity for different instances of different objects including buildings and trees. Motion cues are useful as the scene is highly dynamic with moving objects including vehicles and pedestrians. This work utilizes geometric information modelled by depth maps and motion cues represented by

MDAC: A new reputation system for misbehavior detection and control in ad hoc networks

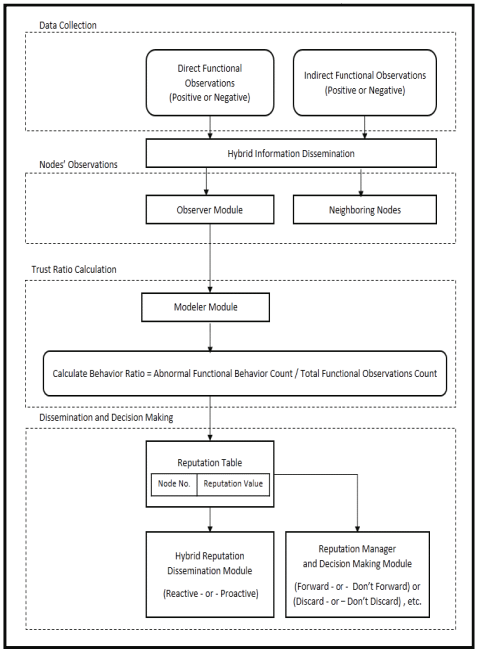

Reputation systems are an emerging area of research in ad-hoc networks. They have been introduced as a security solution for nodes' misbehaving problem. A reputation system should cope with any kind of misbehavior. It enables honest nodes to make fair decisions about their neighbors. This may encourage nodes to behave well and cooperate in order to avoid being penalized or isolated. In this paper, we propose a new reputation system for Misbehavior Detection And Control in ad hoc Networks (MDAC). It aims to overcome some of the unsolved issues of other reputation systems, and it is customizable

Comparison study of digital forensics analysis techniques

Recently, digital forensics analysis got a great attention in IT security. This is especially after cyber incidents are getting new form of organized crime which introduced Advanced Persistent Threats (APT), and hacking Kill Chain definitions. The threat intense rises when it is affecting the healthcare organization where it will be life-threatening. Handling such incidents is a great challenge for handlers to uncover the attack steps. With various sources of evidential data that require analysis, one analysis technique can be more beneficial than another, comparing to the time and resources

Cluster Head election in Wireless Sensor Networks

Wireless Sensor Networks (WSNs) consist of a collection of cheap, easy to deploy Sensor nodes arranged together to fulfill a specific purpose (monitoring, tracking...etc.). A WSN network is composed of a Base Station (BS) and collection of sensors. There are a lot of approaches for the network construction. Amongst them is the hierarchical structure, where the network is divided into clusters and the node inside this cluster communicates with BS through a chosen leader called Cluster Head (CH). In this paper, we present cluster-Head election algorithms for WSNs. We will discuss the operations

Native Mobile Applications UI Code Conversion

With the widespread use of mobile applications in daily life, it has become crucial for software companies to develop the applications for the most popular platforms like Android and iOS. Using a native development is time consuming and costly. Cross-platform mobile development like Xamarin and React native emerged as a solution to the mentioned problem of native development for the time and cost. Meanwhile it requires the developers to learn a new language. Other tools are converting the mobile apps of specific platform to the corresponding platform, but most of them still lack the mobile

ANN-Python prediction model for the compressive strength of green concrete

Purpose: Utilization of sustainable materials is a global demand in the construction industry. Hence, this study aims to integrate waste management and artificial intelligence by developing an artificial neural network (ANN) model to predict the compressive strength of green concrete. The proposed model allows the use of recycled coarse aggregate (RCA), recycled fine aggregate (RFA) and fly ash (FA) as partial replacements of concrete constituents. Design/methodology/approach: The model is constructed, trained and validated using python through a set of experimental data collected from the

INVESTIGATION OF DIFFERENTIALLY EXPRESSED GENE RELATED TO HUNTINGTON'S DISEASE USING GENETIC ALGORITHM

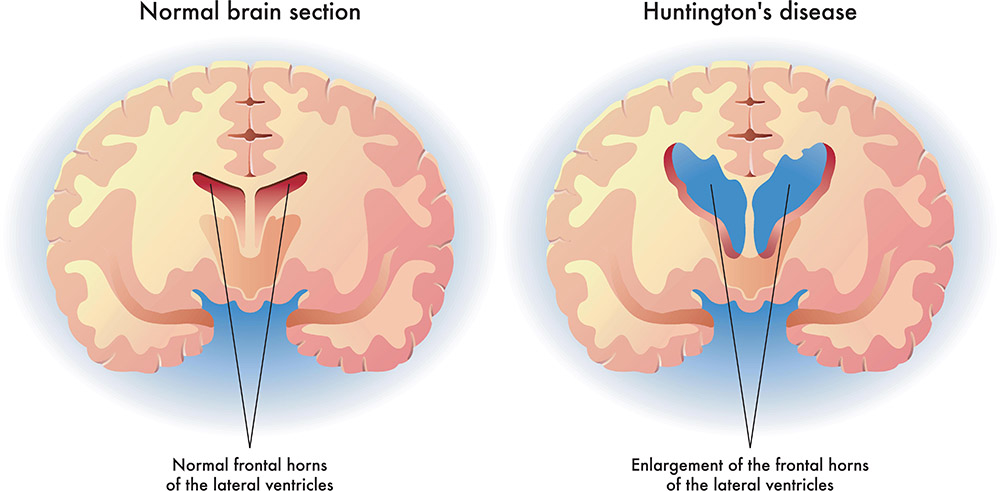

neurodegenerative diseases have complex pathological mechanisms. Detecting disease-associated genes with typical differentially expressed gene selection approaches are ineffective. Recent studies have shown that wrappers Evolutionary optimization methods perform well in feature selection for high dimensional data, but they are computationally costly. This paper proposes a simple method based on a genetic algorithm engaged with the Empirical Bays T-statistics test to enhance the disease-associated gene selection process. The proposed method is applied to Affymetrix microarray data from

Assessing leanness level with demand dynamics in a multi-stage production system

Purpose - The purpose of this paper is to present a dynamic model to measure the degree of system's leanness under dynamic demand conditions using a novel integrated metric. Design/methodology/approach - The multi-stage production system model is based on a system dynamics approach. The leanness level is measured using a new developed integrated metric that combines efficiency,WIP performance as well as service level. The analysis includes design of experiment technique at the initial analysis to examine the most significant parameters impacting the leanness score and then followed by

Simplified modelling for power consumption of base station sites in mobile telecommunications systems

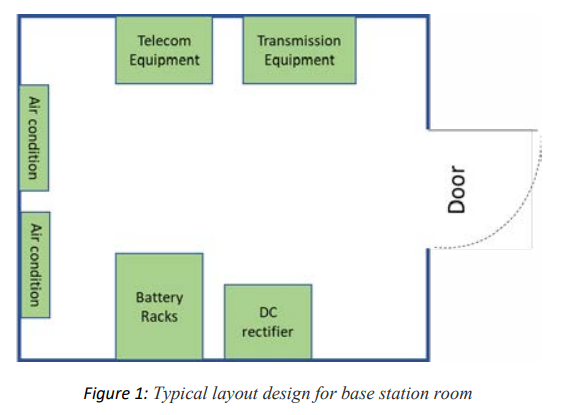

Reducing energy consumption is a global concern for all industries. Modern communications systems facilitate human interactions compared to previous ages. Telecommunications and IT are among the fast-growing industries with rapid demand for more energy. Moreover, the wide adoption of wireless mobile communications applications has resulted in installing massive numbers of Base Station (BS) sites to serve the rapid demand for wider mobile coverage and the growing need for more capacity and speed. These Base Stations are responsible for the major part of the energy needs of mobile wireless

Artificial intelligence for retail industry in Egypt: Challenges and opportunities

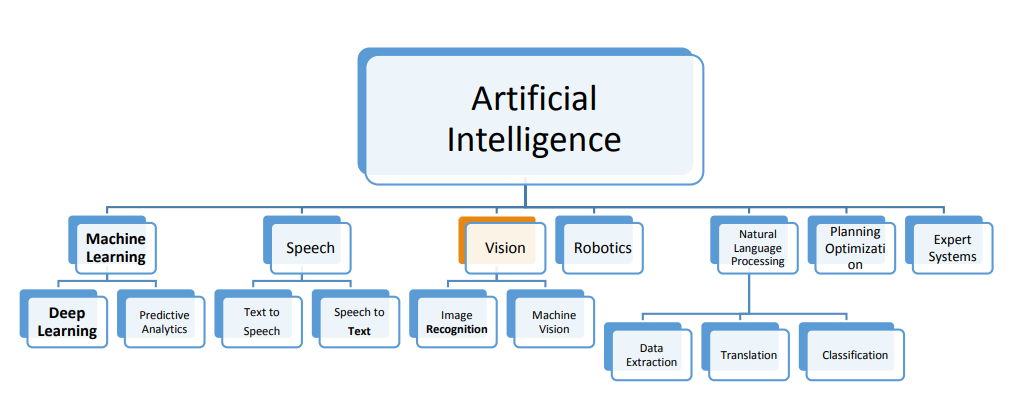

In the era of digital transformation, a mass disruption in the global industries have been detected. Big data, the Internet of Things (IoT) and Artificial Intelligence (AI) are just examples of technologies that are holding such digital disruptive power. On the other hand, retailing is a high-intensity competition and disruptive industry driving the global economy and the second largest globally in employment after the agriculture. AI has large potential to contribute to global economic activity and the biggest sector gains would be in retail. AI is the engine that is poised to drive the

Pagination

- Previous page ‹‹

- Page 8

- Next page ››