Two-port two impedances fractional order oscillators

This paper presents a study for general fractional order oscillator based on two port network where two topologies of oscillator structure with two impedances are discussed. The two impedances are chosen to be fractional elements which give four combinations for each topology. The general oscillation frequency, condition and the phase difference between the two oscillatory outputs are deduced in terms of the transmission matrix parameter of a general two port network. As a case study: two different networks are presented which are op-amp based circuit and non-ideal gyrator circuit. The

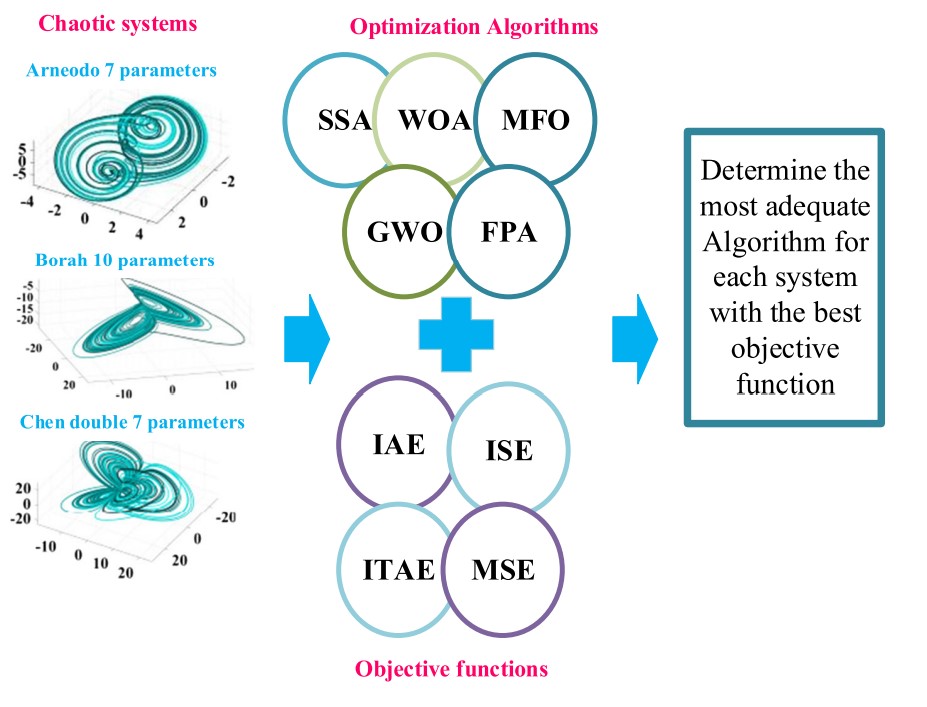

Parameter identification of fractional-order chaotic systems using different Meta-heuristic Optimization Algorithms

Fractional-order chaotic systems (FOCS) parameter identification is an essential issue in chaos control and synchronization process. In this paper, different recent Meta-heuristic Optimization Algorithms are used to estimate the parameters and orders of three FOCS. The investigated systems are Arneodo, Borah rotational attractor and Chen double- and four-wing systems. The employed algorithms are the Salp Swarm Algorithm, Whale Optimization Algorithm, Moth-Flame Optimizer, Grey Wolf Optimizer and the Flower Pollination Algorithm (FPA). The proposed algorithms are applied on several objective

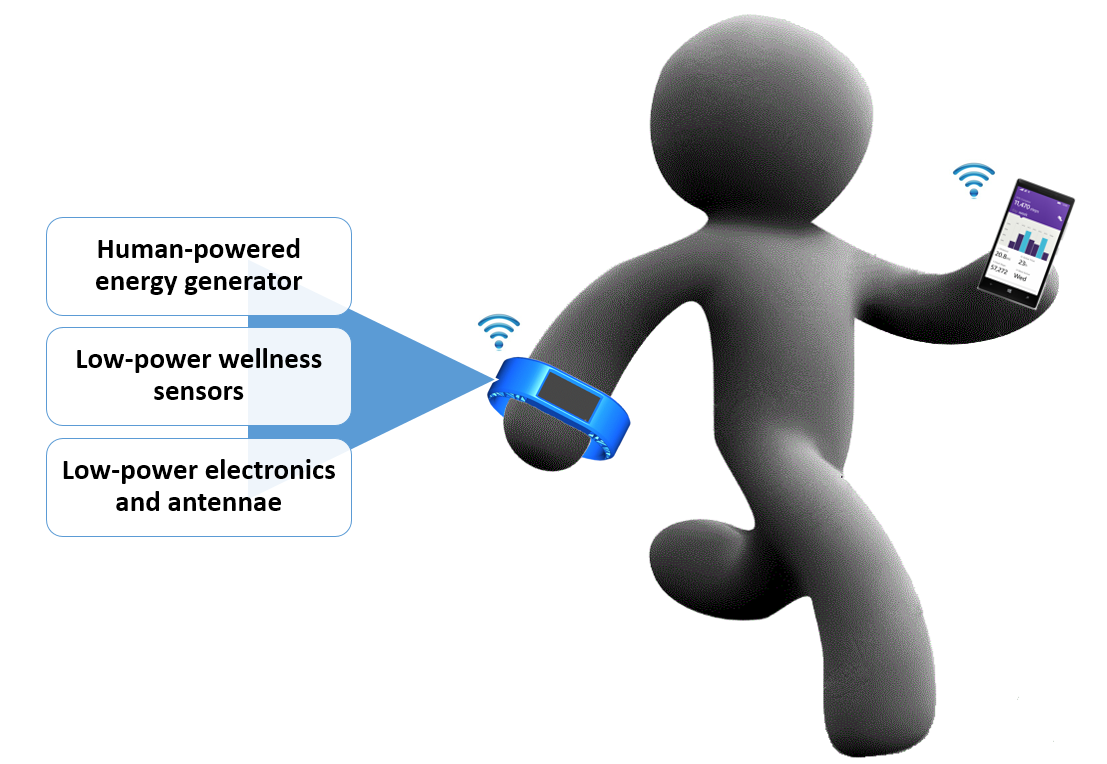

Energy Harvesting Schemes for Wearable Devices

For the specifications of Wireless Body Area Networks (WBANs), eHealth systems, and wearable devices, batteries are not desirable. They maximize the sensor nodes’ size and need to be replaced every few years through human interference. Energy harvesting is now being studied as the primary source of electricity for wearable devices. Several initiatives have succeeded in using energy harvesting to operate the wearable devices’ electronic components. However, to rely primarily on energy harvesting in wearable devices, some obstacles need to be addressed. This work surveys the development of

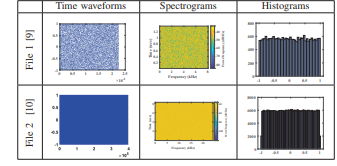

Speech Encryption on FPGA Using a Chaotic Generator and S-Box Table

In this paper, we proposed a new technique for designing a dynamic S-box depended on the idea of DNA module and Chaotic system to increase its security. Lorenz chaotic generator is utilized as the chaos part of the proposed design. This design is Tested on the Field Programmable Gate Array (FPGA) for the use of offline speech encryption and decryption in real time. The experimental results are presented on the oscilloscope. The security of the system is also validated through tests on Matlab. © 2019 IEEE.

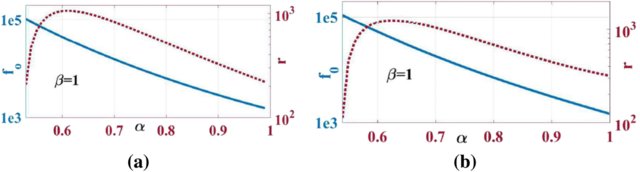

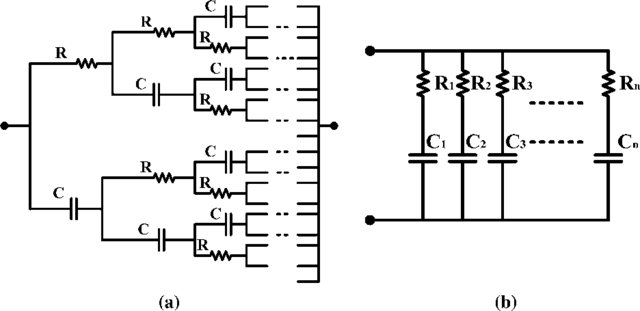

Using Meta-heuristic Optimization to Extract Bio-impedance Parameters from an Oscillator Circuit

This paper introduces a method for extracting the Cole-impedance model parameters using a meta-heuristic optimization technique. The method is based on a single proposed resistor controlled oscillator (SRCO) where the unknown bio-impedance is embedded. At two different oscillation frequencies, the start-up oscillation condition is recorded. Then the corresponding nonlinear equations are solved using the flower pollination optimization (FPA) technique to find the optimum impedance parameters that minimize an objective error function. Experimental results are provided, and comparisons with model

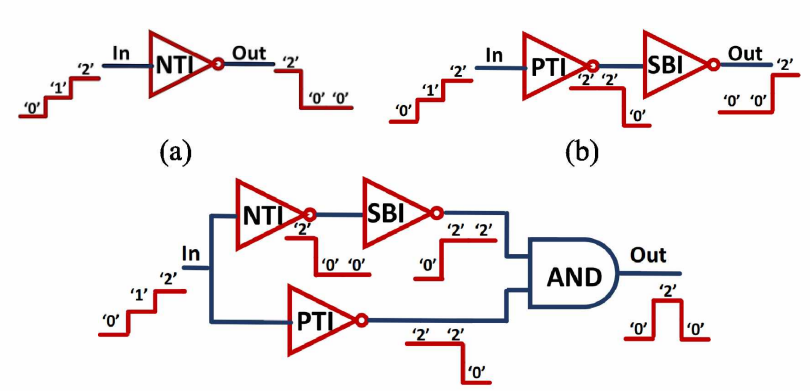

Cad tool for two-digit ternary functions design

Ternary number, which attracts the research attention for its high capacity, has emerged in many applications, recently. Unlike binary numbers, two bit ternary number involves 93 = 729 different functions while two bit binary number involves only 42 = 16 different possible functions. In this paper, a novel automatic software description two bits ternary functions design tool is presented. Different examples are provided and synthesized to ternary logic circuits. Finally, the presented logic circuits are verified by SPICE simulation using carbon nano-Tube (CNTFET) transistors. © 2019 IEEE.

FPGA Speech Encryption Realization Based on Variable S-Box and Memristor Chaotic Circuit

This paper introduces a new encryption/decryption scheme based on a dynamic substitution box concept. Values of the proposed S-Box are different for each sample depending on the behavior of a memristor-based chaotic system. MATLAB simulations and FPGA implementation for the circuit are presented with throughput 4.266 Gbit/s. Also, FPGA realization for encryption/decryption scheme is proposed. Entropy, MSE, correlation coefficient tests are applied on two different input files to examine the efficiency of this cryptosystem. © 2018 IEEE.

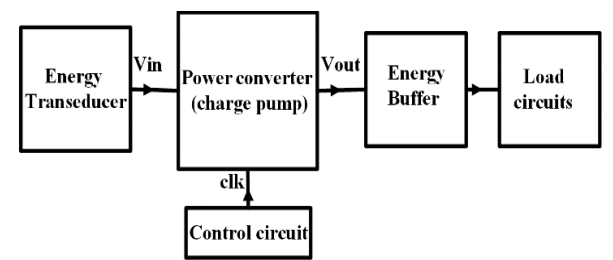

Memcapacitor based charge pump

This paper proposes a charge pump based on a charge controlled memcapacitor. The operation of the charge pump is investigated along with the mathematical analysis of the memcapacitor. Different implementations of charge pump are summarized. The proposed charge pump has the capability of driving low input voltage in range of 200mv and the capability of operating at the low frequencies which makes it suitable for biomedical applications. © 2017 IEEE.

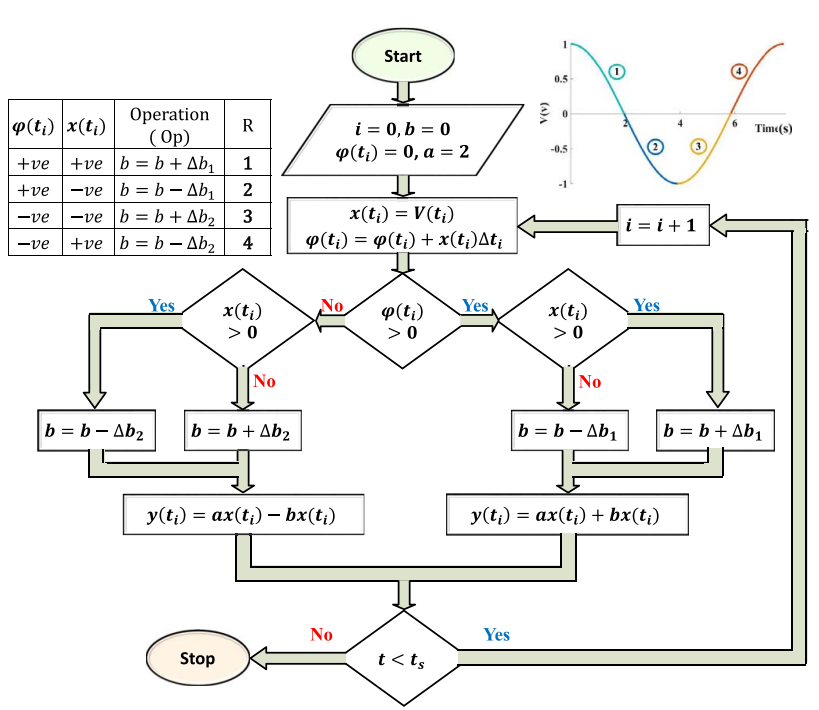

Memristor FPGA IP core implementation for analog and digital applications

Exploring the nonlinear dynamics of the memristors is essential to be adequately used in the applications. Realizing memristor on FPGAs as an intellectual property (IP) core offers a flexible platform to realize different models. In the literature, few implementations have been proposed for simple and limited memristor model. In this brief, two discrete and continuous versatile memristor models alongside their FPGA realizations are proposed. These models can generate different pinched hysteric behaviors, such as symmetric, asymmetric pinched hysteresis, and multi-state switching behavior. In

Memristor-CNTFET based Ternary Comparator unit

This paper proposes a new design for ternary logic comparator unit based on memristive threshold logic concept. To provide high-performance design, integrating memristor and Carbon Nano-Tube Field-Effect Transistor, CNTFET, is used. A comparison with other related work is presented to discuss performance aspects. It shows that performance has been improved by 75% compared with the other related work. Therefore, the proposed design is very promising to build high-performance full ternary ALU memristor-based unit. © 2018 IEEE.

Pagination

- Previous page ‹‹

- Page 59

- Next page ››