Extraction of Phase Information from Magnitude-Only Bio-impedance Measurements Using a Modified Kramers–Kronig Transform

The need for portable and low-cost bio-impedance analyzers that can be deployed in field studies has significantly increased. Due to size and power constraints, reducing the hardware in these devices is crucial and most importantly is removing the need for direct phase measurement. In this paper a new magnitude-only technique based on modified Kramers–Kronig transforms is proposed and tested. Comparison with impedance measurements of fresh and aging tomato samples using a precise industry standard impedance analyzer is carried out and explained. Error and noise analysis of the proposed

Extraction of bioimpedance phase information from its magnitude using a non-uniform Kramers–Kronig transform

A novel non-uniform Kramers–Kronig Transform algorithm for bioimpedance phase extraction is proposed and tested in this work. The algorithm error is studied and compared with a previously proposed phase extraction technique, also based on the Kramers–Kronig transform. Results using simulated datasets and experimental datasets confirm the excellent performance of the algorithm. © 2020, European Biophysical Societies' Association.

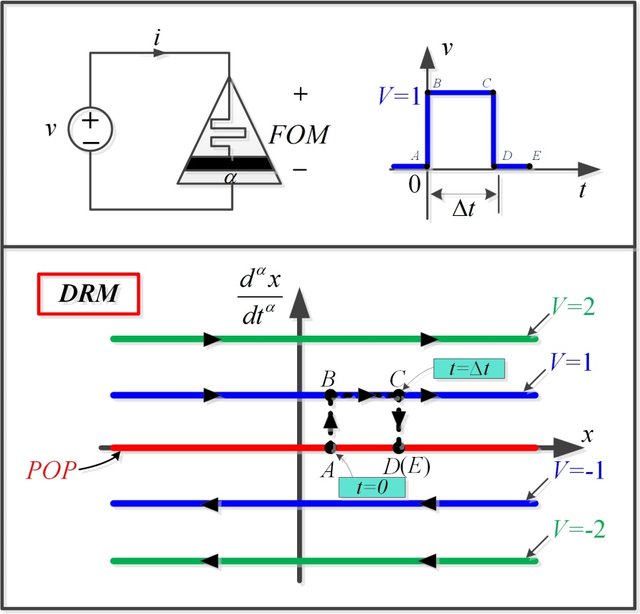

Multiple Pinch-Off Points in Memristive Equations: Analysis and Experiments

Pinched hysteresis behavior is considered evidence of the existence of the memristive element. Recently, the multi-lobes (more than two) behavior has been discovered in some memristive devices. In this paper, a fractional-order flux/voltage-controlled memristive model is introduced that is able to develop multiple symmetric and asymmetric pinch-off points. Generalized closed-form expressions for the necessary conditions of multiple pinch-off points existence are derived in addition to the coordinates of the pinch-off points in the I-V plane. Closed-form expressions for the minimum and maximum

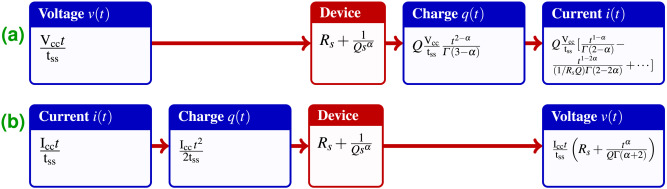

Supercapacitor reciprocity and response to linear current and voltage ramps

The focus in supercapacitor research typically falls into one of two categories: (i) the rational design and engineering of electrode materials and electrolyte formulation to achieve high performance devices at competitive costs, and (ii) the modeling of their resulting behavior in response to constant-current charging/discharging, cyclic voltammetry or impedance spectroscopy. However, less work has been dedicated to new ways for charging these devices. In this work we show that charging a supercapacitor, modeled as a constant phase element with a series resistor, using a linear voltage ramp

Supercapacitor discharge under constant resistance, constant current and constant power loads

Supercapacitors, which are now widely used as power sources in various applications, are discharged with one of the following three basic discharge modes: a constant current load, a constant resistance load or a constant power load. A constant current load is one which varies its internal resistance to achieve a constant current regardless of the applied voltage. For the constant resistance case, it results in a change of power as the voltage level changes. And for a constant power load, the load varies its impedance as the input voltage changes in order to keep the power constant. However

Supercapacitor Fractional-Order Model Discharging from Polynomial Time-Varying Currents

Fractional-order models of supercapacitors are advantageous in that they have fewer terms, offering simpler expressions to accurately describe the transient characteristics of these devices than integer-order models. When evaluating the discharge characteristics of supercapacitors, a constant current is often considered which does necessarily represent real-world applications. In this work, the voltage discharging expressions of a fractional-order model of a supercapacitor to time-varying polynomial discharging currents are presented using simulations to highlight the different cases. In

New hybrid synchronisation schemes based on coexistence of various types of synchronisation between master-slave hyperchaotic systems

In this paper, we present new approaches to study the co-existence of some types of synchronisation between hyperchaotic dynamical systems. The paper first analyses, based on stability theory of linear continuous-Time systems, the co-existence of the projective synchronisation (PS), the function projective synchronisation (FPS), the full state hybrid function projective synchronisation (FSHFPS) and the generalised synchronisation (GS) between general master and slave hyperchaotic systems. Successively, using Lyapunov stability theory, the coexistence of three different synchronisation types is

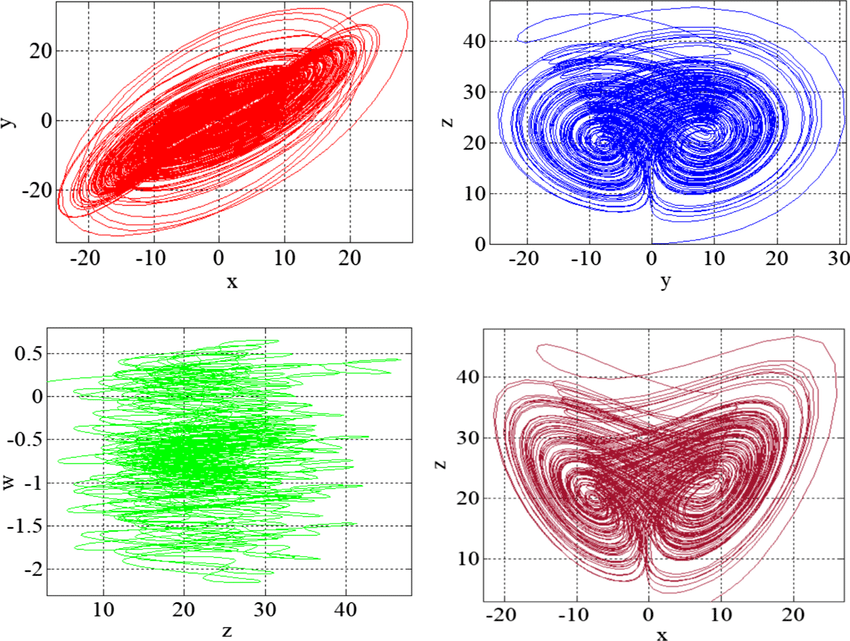

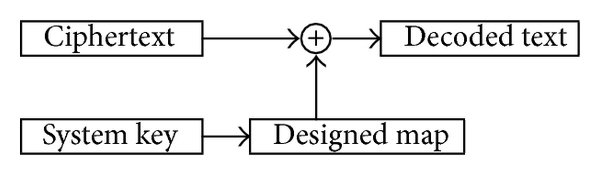

Trajectory control and image encryption using affine transformation of lorenz system

This paper presents a generalization of chaotic systems using two-dimensional affine transformations with six introduced parameters to achieve scaling, reflection, rotation, translation and/or shearing. Hence, the location of the strange attractor in space can be controlled without changing its chaotic dynamics. In addition, the embedded parameters enhance the randomness and sensitivity of the system and control its response. This approach overpasses performing the transformations as post-processing stages by applying them on the resulting time series. Trajectory control through dynamic

Design of Positive, Negative, and Alternating Sign Generalized Logistic Maps

The discrete logistic map is one of the most famous discrete chaotic maps which has widely spread applications. This paper investigates a set of four generalized logistic maps where the conventional map is a special case. The proposed maps have extra degrees of freedom which provide different chaotic characteristics and increase the design flexibility required for many applications such as quantitative financial modeling. Based on the maximum chaotic range of the output, the proposed maps can be classified as positive logistic map, mostly positive logistic map, negative logistic map, and

Improved memristor-based relaxation oscillator

This paper presents an improved memristor-based relaxation oscillator which offers higher frequency and wider tunning range than the existing reactance-less oscillators. It also has the capability of operating on two positive supplies or alternatively a positive and negative supply. Furthermore, it has the advantage that it can be fully integrated on-chip providing an area-efficient solution. On the other hand, The oscillation concept is discussed then a complete mathematical analysis of the proposed oscillator is introduced. Furthermore, the power consumption of the new relaxation circuit is

Pagination

- Previous page ‹‹

- Page 47

- Next page ››