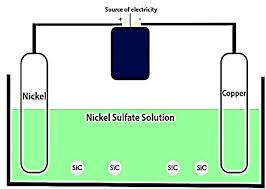

Enhancing CSP using Spot Fresnel Lens and SiC Coating

Concentrated Solar Power (CSP) systems have a good potential as a renewable energy candidate that are based on converting the incident solar thermal energy to an electrical energy. In this paper, CSP using spot Fresnel lens instead of traditional lenses is presented to enhance the efficiency of the system, where Silicon Carbide (SiC) is used as a coating material for the receiver of the system due to its high thermal conductivity. The presented prototype has been investigated for uncoated spot Fresnel lens CSP, and for spot Fresnel lens CSP with the SiC as a coating material showing the

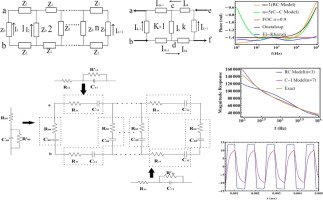

Realization of fractional-order capacitor based on passive symmetric network

In this paper, a new realization of the fractional capacitor (FC) using passive symmetric networks is proposed. A general analysis of the symmetric network that is independent of the internal impedance composition is introduced. Three different internal impedances are utilized in the network to realize the required response of the FC. These three cases are based on either a series RC circuit, integer Cole-impedance circuit, or both. The network size and the values of the passive elements are optimized using the minimax and least m th optimization techniques. The proposed realizations are

Memristor-CNTFET based ternary logic gates

Multilevel electronic systems offer the reduction of implementation’ complexity, power consumption, and area. Ternary system is a very promising system where more information is represented in the same number of digits compared to the binary systems. In this paper, ternary logic gates and some of their ternary circuit applications are presented using memristors and CNTFET inverter. This integration between memristors and CNTFET offers low static power, small area and high performance. The proposed circuits do not require refreshment like the previously published circuits and are not initial

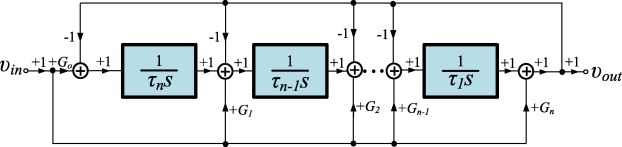

Minimization of Spread of Time-Constants and Scaling Factors in Fractional-Order Differentiator and Integrator Realizations

The approximations of fractional-order differentiator/integrator transfer functions are currently performed using integer-order rational functions, which are in general implemented through appropriate multi-feedback topologies. The spreading in the values of time-constants and scaling factors, needed to implement these topologies, increases as the order of the differentiator/integrator and/or the order of the approximation increases. This leads to non-practical values of capacitances and resistances/transconductances in the implementation. A solution to overcome this obstacle is introduced in

Employment of the Padé approximation for implementing fractional-order lead/lag compensators

Fractional-order lead/lag compensator realizations, using Operational Transconductance Amplifiers as active blocks, are presented in this paper. Two different types of fractional-order transfer functions, derived from the integer-order lead/lag compensator transfer function, are used to describe the behavior of the fractional-order compensator. Both types are approximated using the Padé approximation tool, and are expressed by the same form of rational integer-order transfer function. This means that both types can be implemented using the same active core, which is an important advantage from

Correlation Between the Theory of Lissajous Figures and the Generation of Pinched Hysteresis Loops in Nonlinear Circuits

In this paper, the application of the theory of Lissajous figures to the creation of pinched hysteresis loops, considered to be a characteristic of memristive systems, is demonstrated and experimentally verified using designed electronic circuits in the form of an input impedance. The relationship between the Lissajous-based model of the pinched hysteresis loop and a previously reported integrator-multiplier model is clarified. Important special cases are highlighted and necessary conditions to obtain a pinch point, loops with positive or negative inclination, as well as no pinch point are

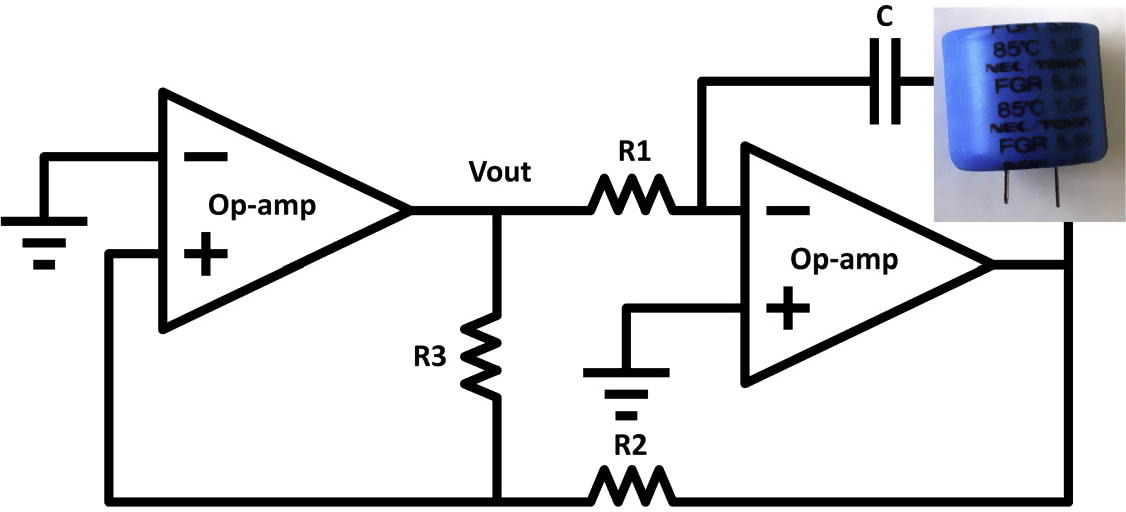

A low frequency oscillator using a super-capacitor

A low frequency relaxation oscillator is designed using a super-capacitor. An accurate analytical expression for the oscillation frequency is derived based on a fractional-order super-capacitor model composed of a resistance in series with a Constant Phase Element (CPE) whose pseudo-capacitance and dispersion coefficient are determined using impedance spectroscopy measurements. Experimental results confirm our theoretical analysis. © 2016 Elsevier GmbH. All rights reserved.

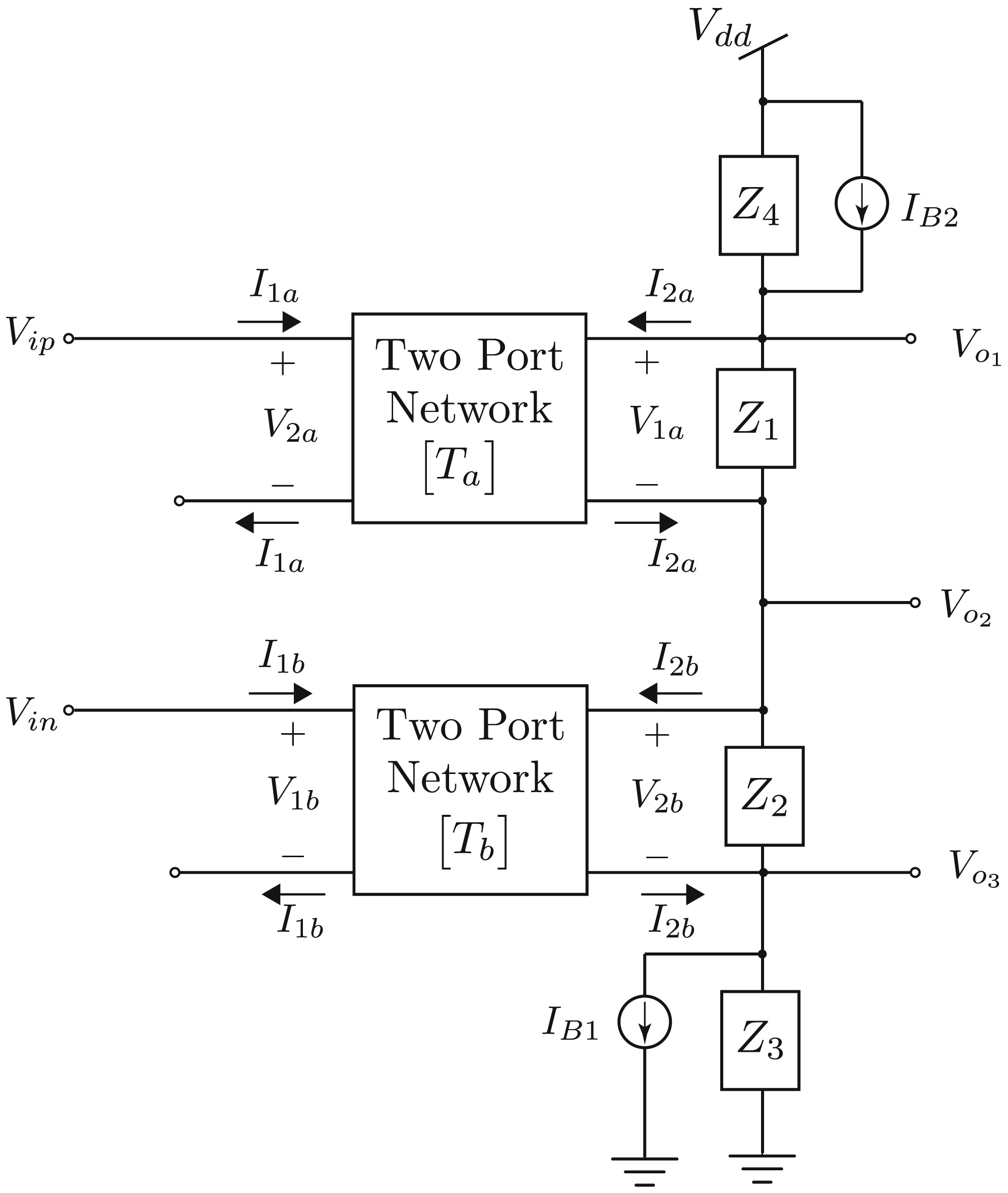

Minimal two-transistor multifunction filter design

This paper presents a comprehensive method and analysis on the design of two-transistor multi-output filters where three possible functions are simultaneously available. Although two transistors are employed at its core, proper biasing does not require additional passive components. A total of thirteen valid second-order filters are reported, and several of them are experimentally tested using discrete transistors as well as simulated using Spectre in a BiCMOS process. A fully differential realization of a MOS-C band-pass filter, based on one of the structures found, is designed and then used

On the Analysis and Design of Fractional-Order Chebyshev Complex Filter

This paper introduces the concept of fractional-order complex Chebyshev filter. A fractional variation of Chebyshev differential equations is introduced based on Caputo fractional operator. The proposed equation is solved using fractional Taylor power series method. The condition for fractional polynomial solutions is obtained and the first four polynomials scaled using an appropriate scaling factor. The fractional-order complex Chebyshev low-pass filter based on the obtained fractional polynomials is developed. Two methods for obtaining the transfer functions of the complex filter are

Software and Hardware Implementation Sensitivity of Chaotic Systems and Impact on Encryption Applications

This paper discusses the implementation sensitivity of chaotic systems added to their widely discussed sensitivities to initial conditions and parameter variation. This sensitivity can cause mismatches in some applications, which require an exact duplication of the system, e.g., chaos-based cryptography, synchronization and communication. Specifically, different implementation cases of three discretized jerk-based chaotic systems and a discrete-time logistic map are presented corresponding to different orders of additions and multiplications. The cases exhibit roughly similar attractor shapes

Pagination

- Previous page ‹‹

- Page 39

- Next page ››