High-Frequency Capacitorless Fractional-Order CPE and FI Emulator

A fractional-order capacitor and inductor emulator, implemented using MOS transistors, instead of passive capacitors, is introduced in this paper. This is achieved using current mirrors as active elements, without passive resistors, and therefore reducing the circuit complexity and resulting in both a resistorless and capacitorless topology. The emulator has been designed by combining fractional-order differentiator or integrator topologies with a voltage-to-current converter. An important benefit from the design flexibility point of view is that the same topology could be used for emulating a

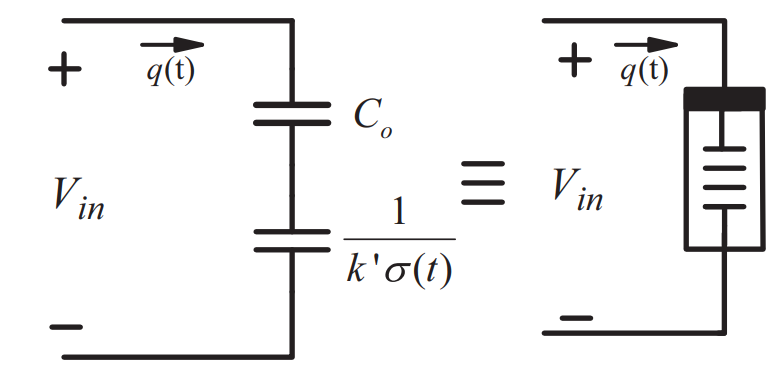

Memcapacitor response under step and sinusoidal voltage excitations

Recently, mem-elements have become fundamental in the circuit theory through promising potential applications based on the built-in memory-properties of these elements. In this paper, the mathematical analysis of the memcapacitor model is derived and the effect of different voltage excitation signals is studied for the linear dopant model. General closed form expressions and analyses are presented to describe the memcapacitor behavior under DC step and sinusoidal voltage excitations. Furthermore, the step and sinusoidal responses are used to analyze the memcapacitor response under any periodic

Synthesis of a family of differential cross-coupled oscillators and design application

A new class of differential oscillators comprising ten possible circuits is introduced in this work. Half of the members of this family are LC-based oscillators and the other half are RC-based ones. While all oscillators are second-order, a maximum of four resistors was imposed as a restriction on possible oscillators that belong to the proposed architecture. Only two of the found oscillators are canonical but all members of the this family have unique and attractive design features. Experimental results using discrete components verify the operation of selected circuits designed for short

Symmetric encryption algorithms using chaotic and non-chaotic generators: A review

This paper summarizes the symmetric image encryption results of 27 different algorithms, which include substitution-only, permutation-only or both phases. The cores of these algorithms are based on several discrete chaotic maps (Arnold's cat map and a combination of three generalized maps), one continuous chaotic system (Lorenz) and two non-chaotic generators (fractals and chess-based algorithms). Each algorithm has been analyzed by the correlation coefficients between pixels (horizontal, vertical and diagonal), differential attack measures, Mean Square Error (MSE), entropy, sensitivity

Hardware Speech Encryption Using a Chaotic Generator, Dynamic Shift and Bit Permutation

This paper proposes a speech encryption and decryption system, its hardware architecture design and FPGA implementation. The system utilizes Nosé Hoover chaotic generator and/or dynamic shift and bit permutation. The effect of different blocks in the proposed encryption scheme is studied and the security of the system is validated through perceptual and statistical tests. The complete encryption scheme is simulated using Xilinx ISE 14.5 and realized on FPGA Xilinx Kintex 7, presenting the experimental results on the oscilloscope. The efficiency is also validated through hardware resources

Memristor-based pulse width modulator circuit

This paper discusses the use of the memristor in one of the most important modulation techniques in communication field namely the pulse-width modulation. A fundamental two designs for memristor-based lead and trail PWM are discussed with mathematical analysis and PSPICE simulation results which show a great matching with the analytical formulation. Moreover, a third design which combine those two designs to generate a more accurate memristor-based center PWM is discussed with the appropriate analysis, numerical and PSPICE simulation results. The simulation results matches the theoretical

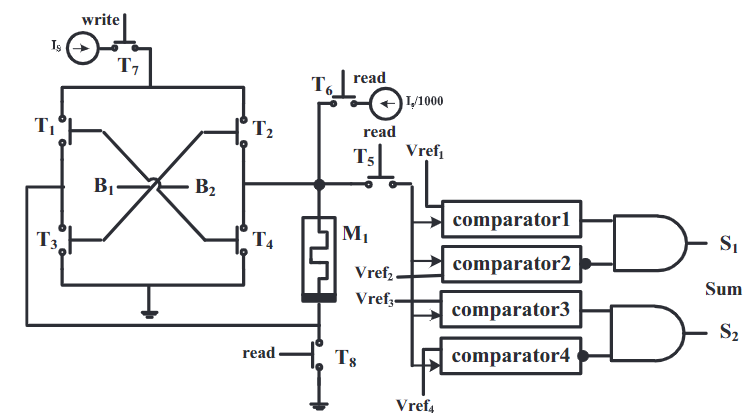

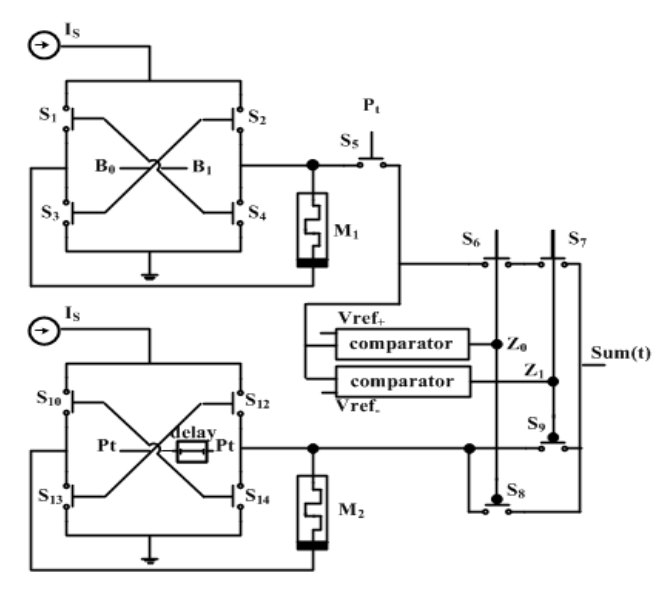

Memristor based N-bits redundant binary adder

This paper introduces a memristor based N-bits redundant binary adder architecture for canonic signed digit code CSDC as a step towards memristor based multilevel ALU. New possible solutions for multi-level logic designs can be established by utilizing the memristor dynamics as a basis in the circuit realization. The proposed memristor-based redundant binary adder circuit tries to achieve the theoretical advantages of the redundant binary system, and to eliminate the carry (borrow) propagation using signed digit representation. The advantage of carry elimination in the addition process is that

Memristor-based redundant binary adder

This paper introduces a memristor based redundant binary adder for canonic signed digit code, that coding eliminates the carry and provides a carry-free addition. The proposed binary adder circuit tries to achieve high addition speed that is independent on the length of the data using the accumulation property of a Nano-element called a memristor. The general block diagram of the proposed circuit is illustrated based on memristors and its operation has been validated using HP memristor model and simulated via different examples using PSPICE showing a great match. © 2014 IEEE.

Hermite polynomials in the fractional order domain suitable for special filters design

Due to the importance of its integer order counterpart in many mathematical and engineering fields, the fractional order Hermite polynomials are studied in this paper. A fractional variation of the well known Hermite differential equation is introduced based on Caputo fractional operator. The proposed equation is solved using fractional Taylor power series method and the convergence is verified using truncated series for different values of the parameters. The condition for fractional polynomial solution is obtained and the first four polynomials are scaled using an appropriate scaling factor

High Speed, Approximate Arithmetic Based Convolutional Neural Network Accelerator

Convolutional Neural Networks (CNNs) for Artificial Intelligence (AI) algorithms have been widely used in many applications especially for image recognition. However, the growth in CNN-based image recognition applications raised challenge in executing millions of Multiply and Accumulate (MAC) operations in the state-of-The-Art CNNs. Therefore, GPUs, FPGAs, and ASICs are the feasible solutions for balancing processing speed and power consumption. In this paper, we propose an efficient hardware architecture for CNN that provides high speed, low power, and small area targeting ASIC implementation

Pagination

- Previous page ‹‹

- Page 45

- Next page ››