Breadcrumb

Realization of fractional-order capacitor based on passive symmetric network

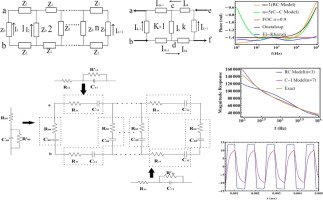

In this paper, a new realization of the fractional capacitor (FC) using passive symmetric networks is proposed. A general analysis of the symmetric network that is independent of the internal impedance composition is introduced. Three different internal impedances are utilized in the network to realize the required response of the FC. These three cases are based on either a series RC circuit, integer Cole-impedance circuit, or both. The network size and the values of the passive elements are optimized using the minimax and least m th optimization techniques. The proposed realizations are compared with well-known realizations achieving a reasonable performance with a phase error of approximately 2 o . Since the target of this emulator circuit is the use of off-the-shelf components, Monte Carlo simulations with 5% tolerance in the utilized elements are presented. In addition, experimental measurements of the proposed capacitors are preformed, therein showing comparable results with the simulations. The proposed realizations can be used to emulate the FC for experimental verifications of new fractional-order circuits and systems. The functionality of the proposed realizations is verified using two oscillator examples: a fractional-order Wien oscillator and a relaxation oscillator. © 2019