Breadcrumb

Parallel feedback compensation for LDO voltage regulators

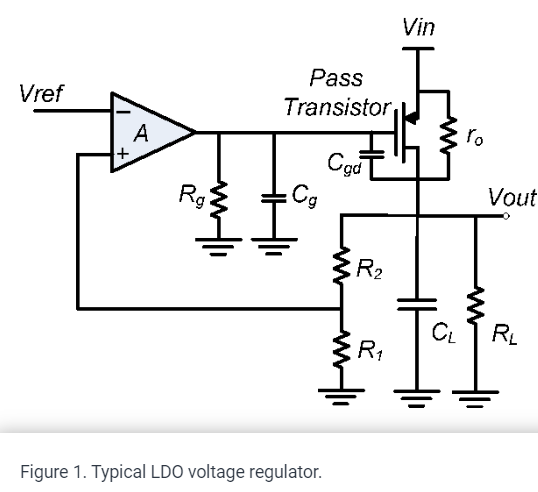

A novel low dropout (LDO) voltage regulator compensation technique is demonstrated. A parallel feedback path is used to insert a zero at approximately three times the output pole. The parallel feedback consists of passive elements only and occupies small area. The proposed technique completely eliminates the output pole at different load conditions and results in high LDO bandwidth, which achieves fast output tracking of the input reference and fast recovery of sudden load changes. Moreover, the output pole elimination at different load conditions enables the potential scaling of the error amplifier quiescent current with the load without compromising stability. The proposed LDO has been implemented in 65-nm TSMC low-power CMOS process, and achieves 0.24-ns response time at 94% current efficiency. For a 1.2-V input voltage and 1-V output voltage the regulator enables 79mVp-p output droop for a maximum load step. ©2010 IEEE.