A novel 10-Bit high-throughput two-stage TDC with reduced power and improved linearity

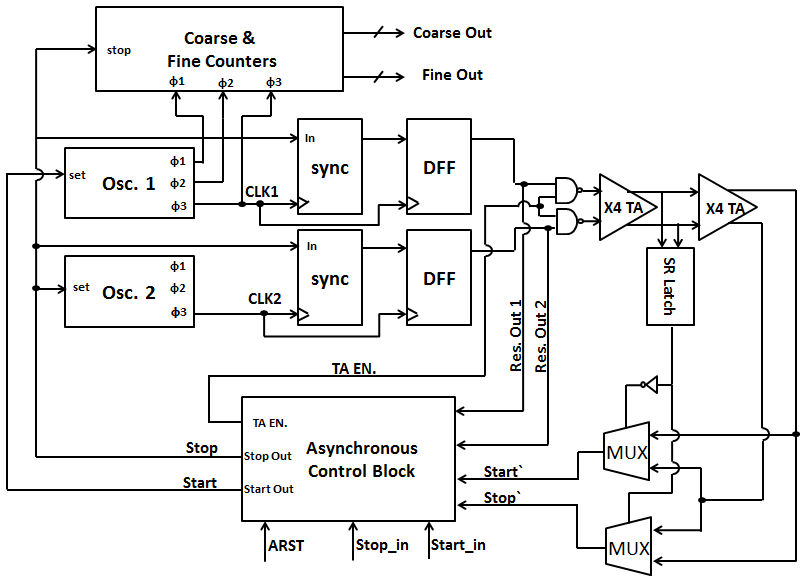

This paper introduces a new architecture that improves the throughput of the two-stage Time to Digital Converter (TDC). An oscillator-based TDC is used for conversion. The time residue from the first stage is generated directly after the stop signal is asserted and saved in the form of phase-shift between two oscillating signals. Instead of using two stages, an asynchronous control block is implemented to reuse the same hardware block for both the first and second conversion stages. This technique not only reduces power and area, but also eliminates the TDC nonlinearity due to the mismatch between the two stages. A throughput of 400 MS/s for a 10bit resolution, a time resolution of 2.6 ps, a DNL of 0.38, and an INL of 0.402 are achieved. © 2013 IEEE.