A 16Gbps low power self-timed SerDes transceiver for multi-core communication

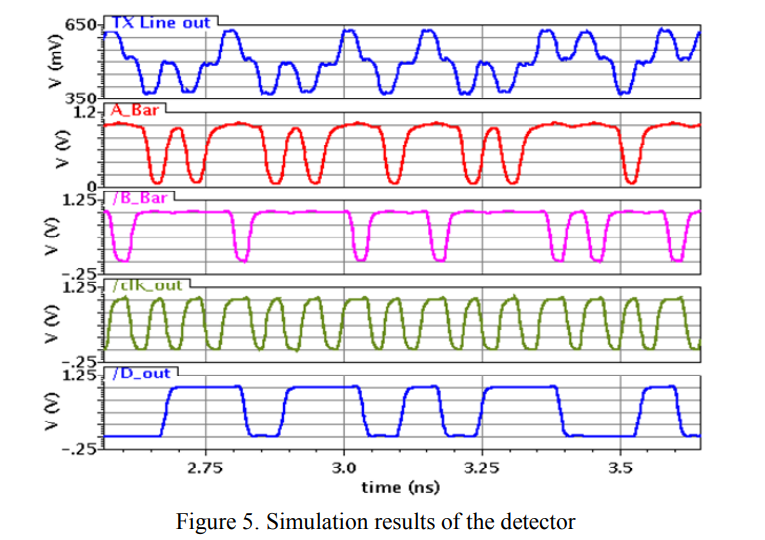

This paper presents a modified design for a self-timed SerDes transceiver that was recently published [1]. The new architecture overcomes the main problems that arise in [1], while offering the same advantages. Resistive termination is used instead of source matching to eliminate the need for Manchester coding in [1], this resistive termination increased the data rate to be 16Gbps compared to 12Gbps in [1]. Moreover, resistive termination removed the limitation on the minimum operating frequency that existed in [1], solving a lot of problems at the slow process corners. A single ended transmission line is used instead of the differential transmission line in [1]. A calibration circuit is implemented to control the switching threshold of the detector at the receiver side to account for voltage and process variations. The SerDes transceiver is implemented for a 3mm long on-chip transmission line in 65nm TSMC CMOS technology, which is the same as [1]. The total power consumed in the Tx/Rx pair with the transmission line is 18.1mWatt, compared to 15.5mWatt in [1]. The proposed architecture have the same advantages in [1] of being self timed, eliminating the need for complex power hungry blocks such as Clock and Data Recovery (CDR) at the receiver, and being insensitive to jitter accumulated during transmission. © 2012 IEEE.